# CS4304P/8P DAC Output Summing Guide

#### Introduction

The CS4304P/8P high-performance DAC devices provide a differential current-mode output that require external components for current-to-voltage (I-to-V) conversion and out-of-band noise filtering. The CS4304P/8P supports the option to combine the DAC signal paths in groups of two, four or a single group of eight channels (eight channels only supported on CS4308P).

This App Note describes the selection of external components for the I-to-V output buffer stage, and the performance improvements that can be achieved using the output-summing configuration.

#### **Table of Contents**

| 1 C | DAC Output Summing                           | . 2 |

|-----|----------------------------------------------|-----|

|     | External Components                          |     |

|     | Recommended Components                       |     |

|     | DACs Combined in Groups of 2                 |     |

|     | DACs Combined in Groups of 4                 |     |

|     | DACs Combined in a Group of 8 (CS4308P only) |     |

|     | Povision History                             | Ω   |

# 1 DAC Output Summing

The CS4304P/8P supports the option to combine the DAC outputs in groups of two, four, or a single group of eight (CS4308P only); this can be used to achieve enhanced dynamic-range performance on the respective paths. A six-channel summing mode is also supported, with DAC1–DAC4 operating in pairs, with DAC5–DAC8 operating individually (CS4308P only).

In the summing configuration, the signal paths are routed and controlled differently to normal operation. The input signals are routed to groups of two or more DACs (depending on the selected configuration), and the grouped paths are each controlled as a single channel.

The DAC output summing is configured using the OUT\_SUM\_MODE field, as described in the CS4304P/8P datasheet (Section 4.5.3). The summing configurations for CS4304P are described in Table 1.

Table 1 CS4304P DAC Output Summing

| Configuration                   | Description     | OUT_SUM_MODE | Output Summing Configuration    | Summed<br>Channel<br>Number |

|---------------------------------|-----------------|--------------|---------------------------------|-----------------------------|

| Default                         | 4-channel       | 0x0          | OUT1-OUT4 as individual outputs | 1–4                         |

| DACs combined in groups of two  | 2-channel input | 0x1          | OUT1+OUT2<br>OUT3+OUT4          | 1<br>2                      |

| DACs combined in groups of four | 1-channel input | 0x2          | OUT1+OUT2+OUT3+OUT4             | 1                           |

The summing configurations for CS4308P are described in Table 2.

Table 2 CS4308P DAC Output Summing

| Configuration                          | Description     | OUT_SUM_MODE | Output Summing Configuration                              | Summed<br>Channel |

|----------------------------------------|-----------------|--------------|-----------------------------------------------------------|-------------------|

| Configuration                          | Description     | OUT_SUM_MODE | Output Summing Configuration                              | Number            |

| Default                                | 8-channel       | 0x0          | OUT1-OUT8 as individual outputs                           | 1–8               |

| DACs combined in groups of two         | 4-channel input | 0x1          | OUT1+OUT2<br>OUT3+OUT4<br>OUT5+OUT6<br>OUT7+OUT8          | 1<br>2<br>3<br>4  |

| DACs combined in groups of four        | 2-channel input | 0x2          | OUT1+OUT2+OUT3+OUT4<br>OUT5+OUT6+OUT7+OUT8                | 1<br>2            |

| DACs combined in<br>groups of<br>eight | 1-channel input | 0x3          | OUT1+OUT2+OUT3+OUT4+OUT5+OUT6+OUT7+OUT8                   | 1                 |

| Four DACs combined in groups of two    | 6-channel input | 0x4          | OUT1+OUT2<br>OUT3+OUT4<br>OUT5–OUT8 as individual outputs | 1<br>2<br>3-6     |

In summing configuration, the respective analog output connections must be combined externally to achieve the performance enhancement. The analog outputs are current-mode outputs; the external combining of these outputs results in the summing of the respective output signals.

Note that the increased current in the summing configuration affects the choice of components for the output buffer, as described in the following section.

#### 1.1 External Components

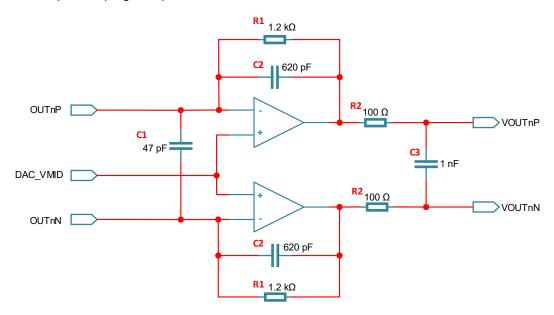

The analog output paths are supported using an external I-to-V output buffer/filter circuit. The recommended external components for the CS4304P/8P output buffer/filter circuit are shown in Figure 1; this circuit produces a 2 V<sub>RMS</sub> differential output from a full-scale (0 dBFS) digital input.

Figure 1: Typical CS4304P/8P Differential Output Buffer/Filter Circuit

The full-scale output voltage is determined by the feedback resistor R1. The required value of R1 also depends on whether the outputs are configured in a summing configuration. The value of R1 can be calculated using the following equation:

$$R_1(k\Omega) = \frac{Full\_scale \ output \ voltage \ (V_{RMS})}{(Numer \ of \ outputs \ summed \ x \ 1.66)}$$

**Note:** The number of outputs summed is 1, 2, 4, or 8 depending on the applicable summing configuration.

The required value of R1 is shown in Table 3 for a range of typical operating configurations. The THD+N performance may be degraded with increased full-scale output voltage. It must also be considered that low resistance (e.g.,  $150~\Omega$ ) may be incompatible with some op-amp devices.

Table 3 Feedback Resistor (R1) Selection

| Configuration    | Full-Scale Output Voltage |                    |                    |

|------------------|---------------------------|--------------------|--------------------|

|                  | 2 V <sub>RMS</sub>        | 4 V <sub>RMS</sub> | 8 V <sub>RMS</sub> |

| No Summing       | 1.2 kΩ                    | 2.4 kΩ             | 4.8 kΩ             |

| 2 outputs summed | 600 Ω                     | 1.2 kΩ             | 2.4 kΩ             |

| 4 outputs summed | 300 Ω                     | 600 Ω              | 1.2 kΩ             |

| 8 outputs summed | 150 Ω                     | 300 Ω              | 600 Ω              |

A low-pass filter is provided using R1 and C2. The filter should be designed to provide a flat passband for the audio bandwidth, while attenuating out-of-band noise. The -3 dB cut-off frequency ( $F_C$ ) can be calculated using the following equation:

$$F_C = \frac{1}{2\pi R_1 C_2}$$

The recommended value of C2 is shown in Table 4 for different values of R1. The recommended configuration provides a –3 dB cut-off around 220 Hz.

Table 4 Feedback Capacitor (C2) Selection

| Resistor | Capacitor | -3 dB Cutoff |  |

|----------|-----------|--------------|--|

| 4.8 kΩ   | 150 pF    | 221 kHz      |  |

| 2.4 kΩ   | 300 pF    | 221 kHz      |  |

| 1.2 kΩ   | 620 pF    | 214 kHz      |  |

| 600 Ω    | 1.2 nF    | 221 kHz      |  |

| 300 Ω    | 2.4 nF    | 221 kHz      |  |

| 150 Ω    | 4.7 nF    | 226 kHz      |  |

Additional filtering is provided using R2 and C3. The recommended components attenuate out-of-band noise, while minimizing the capacitive loading on the op-amp device. Using the values shown, the -3 dB cut-off frequency ( $F_C$ ) can be calculated using the following equation:

$$F_C = \frac{1}{2\pi R_2 2C_3} = \frac{1}{2 \times \pi \times 100 \times 2 \times 1 \times 10^{-9}} = 795.8 \text{ kHz}$$

The recommended value of C1 is 47 pF, assuming output summing is not used. If the outputs are configured in a summing configuration, C1 should be increased to 100 pF.

Table 5 C1 Capacitor Selection

| Configuration                   | Capacitor |

|---------------------------------|-----------|

| No Summing                      | 47 pF     |

| 2 outputs summed                | 100 pF    |

| 4 outputs summed                | 100 pF    |

| 8 outputs summed (CS4308P only) | 100 pF    |

# 1.2 Recommended Components

To achieve the specified performance characteristics, the choice of external components should observe the following recommendations:

- Capacitors should be stable dielectric types, such as C0G (NP0) or electrolytic.

- Resistors should be low value where possible, to minimize thermal noise.

- Low-noise op-amps should be used, such as Texas Instruments OP1656. The op-amps should meet the minimum performance requirements noted in Table 6.

**Table 6 Op-Amp Specification**

| Parameter                    | Specification |

|------------------------------|---------------|

| Input Noise                  | 5 nV/√Hz      |

| Unity Gain bandwidth (G = 1) | 15 MHz        |

| Slew Rate                    | 5 V/μs        |

| THD+N                        | -128 dB       |

Copyright @ 2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

### 1.3 DACs Combined in Groups of 2

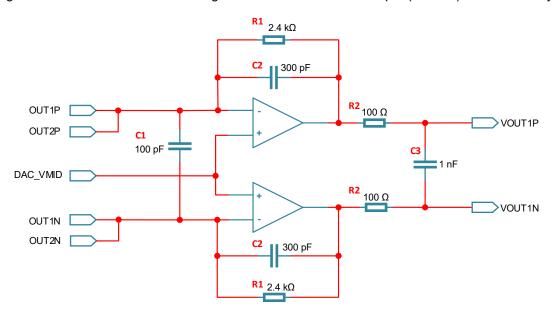

If the DAC outputs are summed in groups of 2 (OUT\_SUM\_MODE = 0x1), the respective groups of analog outputs from the CS4304P/8P must be linked to provide a single output.

The recommended external components for the CS4304P/8P output buffer/filter circuit, when combining 2 DAC outputs, are shown in Figure 2. Note that the circuit is configured for 8 V<sub>RMS</sub> full-scale output (0 dBFS) to maximize dynamic range.

Figure 2: Output Buffer/Filter Circuit - DACs Combined in Groups of 2

The key performance metrics for this summing configuration are shown in Table 7. Comparative figures for the typical no-summing configuration (see Section 1.1) are also shown.

Table 7: Performance Measurements - DACs Combined in Groups of 2

| Measurement              | No Summing (2V full-scale output) | DACs Combined in Groups of 2<br>(8V full-scale output) |

|--------------------------|-----------------------------------|--------------------------------------------------------|

| Signal to Noise Ratio    | 121 dB                            | 123 dB                                                 |

| THD +N Ratio at 0 dBFS   | -115 dB                           | -115 dB                                                |

| Dynamic Range A-weighted | 123 dB                            | 125 dB                                                 |

#### 1.4 DACs Combined in Groups of 4

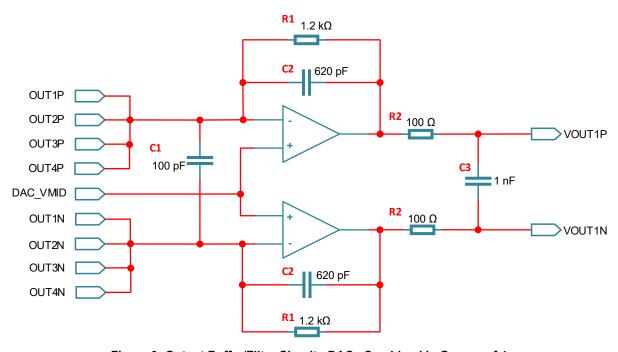

If the DAC outputs are summed in groups of 4 (OUT\_SUM\_MODE = 0x2), the respective groups of analog outputs from the CS4304P/8P must be linked to provide a single output.

The recommended external components for the CS4304P/8P output buffer/filter circuit, when combining 4 DAC outputs, are shown in Figure 3. Note that the circuit is configured for 8 V<sub>RMS</sub> full-scale output (0 dBFS) to maximize dynamic range.

Figure 3: Output Buffer/Filter Circuit - DACs Combined in Groups of 4

The key performance metrics for this summing configuration are shown in Table 8. Comparative figures for the typical no-summing configuration (see Section 1.1) are also shown.

Table 8: Performance Measurements - DACs Combined in Groups of 4

| Measurement              | No Summing (2V full-scale output) | DACs Combined in Groups of 4<br>(8V full-scale output) |

|--------------------------|-----------------------------------|--------------------------------------------------------|

| Signal to Noise Ratio    | 121 dB                            | 125 dB                                                 |

| THD +N Ratio at 0 dBFS   | -115 dB                           | -115 dB                                                |

| Dynamic Range A-weighted | 123 dB                            | 127 dB                                                 |

## 1.5 DACs Combined in a Group of 8 (CS4308P only)

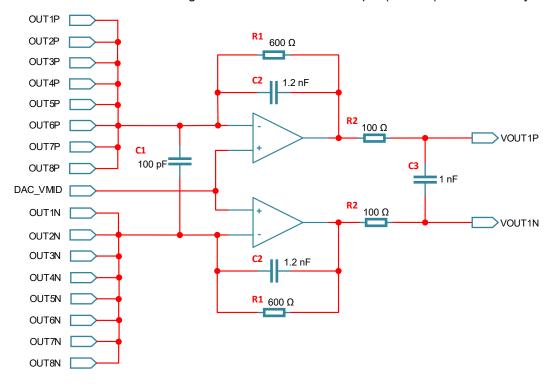

If the DAC outputs are summed in a group of 8 (OUT\_SUM\_MODE = 0x3), the respective groups of analog outputs from the CS4308P must be linked to provide a single output.

The recommended external components for the CS4308P output buffer/filter circuit, when combining 8 DAC outputs, are shown in Figure 4. Note that the circuit is configured for 8 V<sub>RMS</sub> full-scale output (0 dBFS) to maximize dynamic range.

Figure 4: Output Buffer/Filter Circuit - DACs Combined in a Group of 8

The key performance metrics for this summing configuration are shown in Table 9. Comparative figures for the typical no-summing configuration (see Section 1.1) are also shown.

Table 9: Performance Measurements - DACs Combined in a Group of 8

| Measurement              | No Summing (2V full scale output) | DACs Combined in a Group of 8 (8V full-scale output) |

|--------------------------|-----------------------------------|------------------------------------------------------|

| Signal to Noise Ratio    | 121 dB                            | 127 dB                                               |

| THD +N Ratio at -1dBFS   | -115 dB                           | -115 dB                                              |

| Dynamic Range A-weighted | 123 dB                            | 129 dB                                               |

# 2 Revision History

| Revision | Changes          |

|----------|------------------|

| R1       | Initial version. |

| AUG 2025 |                  |

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find the one nearest you, go to www.cirrus.com.

#### **IMPORTANT NOTICE**

The products and services of Cirrus Logic International (UK) Limited; Cirrus Logic, Inc.; and other companies in the Cirrus Logic group (collectively either "Cirrus Logic" or "Cirrus") are sold subject to Cirrus Logic's terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. Software is provided pursuant to applicable license terms. Cirrus Logic reserves the right to make changes to its products and specifications or to discontinue any product or service without notice. Customers should therefore obtain the latest version of relevant information from Cirrus Logic to verify that the information is current and complete. Testing and other quality control techniques are utilized to the extent Cirrus Logic deems necessary. Specific testing of all parameters of each device is not necessarily performed. In order to minimize risks associated with customer applications, the customer must use adequate design and operating safeguards to minimize inherent or procedural hazards. Cirrus Logic is not liable for applications assistance or customer product design. The customer is solely responsible for its overall product design, end-use applications, and system security, including the specific manner in which it uses Cirrus Logic components. Certain uses or product designs may require an intellectual property license from a third party. Features and operations described herein are for illustrative purposes only and do not constitute a suggestion or instruction to adopt a particular product design or a particular mode of operation for a Cirrus Logic component.

CIRRUS LOGIC PRODUCTS ARE NOT DESIGNED, TESTED, INTENDED OR WARRANTED FOR USE (1) WITH OR IN IMPLANTABLE PRODUCTS OR FDA/MHRA CLASS III (OR EQUIVALENT CLASSIFICATION) MEDICAL DEVICES, OR (2) IN ANY PRODUCTS, APPLICATIONS OR SYSTEMS, INCLUDING WITHOUT LIMITATION LIFE-CRITICAL MEDICAL EQUIPMENT OR SAFETY OR SECURITY EQUIPMENT, WHERE MALFUNCTION OF THE PRODUCT COULD CAUSE PERSONAL INJURY, DEATH, SEVERE PROPERTY DAMAGE OR SEVERE ENVIRONMENTAL HARM. INCLUSION OF CIRRUS LOGIC PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS LOGIC DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS LOGIC PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS LOGIC PRODUCTS IN SUCH A MANNER, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS LOGIC, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

This document is the property of Cirrus Logic, and you may not use this document in connection with any legal analysis concerning Cirrus Logic products described herein. No license to any technology or intellectual property right of Cirrus Logic or any third party is granted herein, including but not limited to any patent right, copyright, mask work right, or other intellectual property rights. Any provision or publication of any third party's products or services does not constitute Cirrus Logic's approval, license, warranty or endorsement thereof. Cirrus Logic gives consent for copies to be made of the information contained herein only for use within your organization with respect to Cirrus Logic integrated circuits or other products of Cirrus Logic, and only if the reproduction is without alteration and is accompanied by all associated copyright, proprietary and other notices and conditions (including this notice). This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. This document and its information is provided "AS IS" without warranty of any kind (express or implied). All statutory warranties and conditions are excluded to the fullest extent possible. No responsibility is assumed by Cirrus Logic for the use of information herein, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. Cirrus Logic, Cirrus, the Cirrus Logic logo design, and SoundClear are among the trademarks of Cirrus Logic. Other brand and product names may be trademarks or service marks of their respective owners.

Copyright © 2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd. All rights reserved.