# CS40L5x Configuration User Guide

### Introduction

This user guide describes the functionality, features and configurations that are supported in the CS40L5x Advanced Haptic Driver with Waveform Memory DSP and Closed-Loop Algorithms. This user guide is applicable to the CS40L51, CS40L52, and the CS40L53 devices. For information on the configuration of the CS40L50 device, please see the CS40L50 configuration user guide.

### **Table of Contents**

| Introduction                               | 1  |

|--------------------------------------------|----|

| Table of Contents                          | 1  |

| 1 Power Configuration                      | 2  |

| 1.1 Power Supply Configurations            | 2  |

| 1.1.1 Low Power Rails: Device Supply       |    |

| 1.1.2 High Power Rail: Amplifier Supply    |    |

| 1.2 Operational States                     |    |

| 1.2.1 Reset State                          | 6  |

| 1.2.2 Hibernate State                      |    |

| 1.2.2.1 Wakeup Sources                     |    |

| 1.2.3 Standby State                        | 8  |

| 1.2.4 Active State                         |    |

| 1.2.5 Operating State Transition examples  | 9  |

| 2 Firmware                                 |    |

| 2.1 Initialization Sequence                | 10 |

| 2.1.1 ROM Firmware                         | 10 |

| 2.1.2 RAM Firmware                         | 10 |

| 2.2 Interrupt                              | 10 |

| 2.2.1 Hardware Interrupts                  | 11 |

| 2.2.2 Firmware Interrupts                  | 13 |

| 3 Haptic Playback                          | 15 |

| 3.1 Haptic Wavetables                      | 16 |

| 3.1.1 ROM Waveform                         | 17 |

| 3.1.2 RAM Wavetable                        | 17 |

| 3.1.3 Runtime Haptics Waveforms            | 19 |

| 3.2 Triggering Options                     | 19 |

| 3.2.1 I <sup>2</sup> C/SPI Mailbox Trigger | 20 |

| 3.2.2 GPI Trigger                          | 20 |

| 4 Device Features (Algorithms)             | 21 |

| 4.1 Click Compensation                     | 22 |

| 4.2 Calibration                            | 26 |

| 4.3 Dynamic F0                             | 27 |

| 4.4 Runtime Haptics (RTH)                  | 28 |

| 4.4.1 RTH Registers                        | 29 |

| 4.4.2 RTH PCM Register Format              | 30 |

| 4.4.3 RTH PWLE Register Format             | 32 |

| 4.5 Load Diagnostics                       | 37 |

| 4.6 Generic Haptic System Controls         |    |

| 5 Revision History                         | 39 |

#### **Important Notice:**

No license to any intellectual property right is included with this component, and certain uses or product designs, including certain haptics-related uses or haptics-system designs, may require an intellectual property license from one or more third parties.

# 1 Power Configuration

### 1.1 Power Supply Configurations

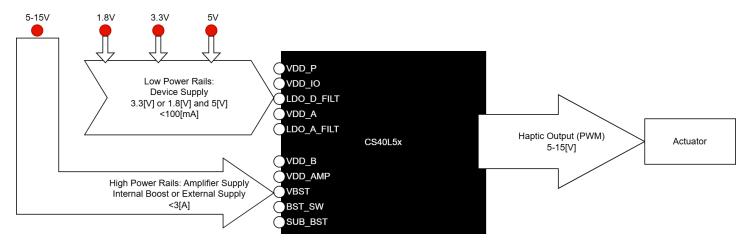

The CS40L5x device supports a variety of power-supply configurations. The power-supply configuration may require register settings during device initialization; the required settings are downloaded by the host processor after power-up. Low power rails include system supply (VDD\_P), digital input/output supply (VDD\_IO), analog supply (VDD\_A). The high-power rail provides the amplifier supply. For details about component rating and layout, see the schematic and layout guidelines.

**Figure 1 Power Supply Configurations**

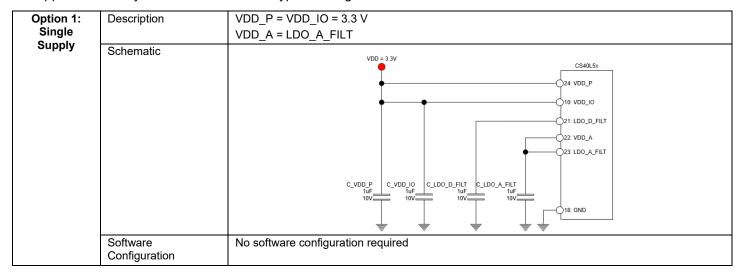

### 1.1.1 Low Power Rails: Device Supply

VDD\_P and VDD\_IO must be supplied externally. VDD\_A can be supplied internally by an LDO; alternatively, VDD\_A can be supplied externally. Below are shown the typical configurations.

Note - All power supplies must be stable prior to release of the RESET pin. See Section 1.2.1 for more details.

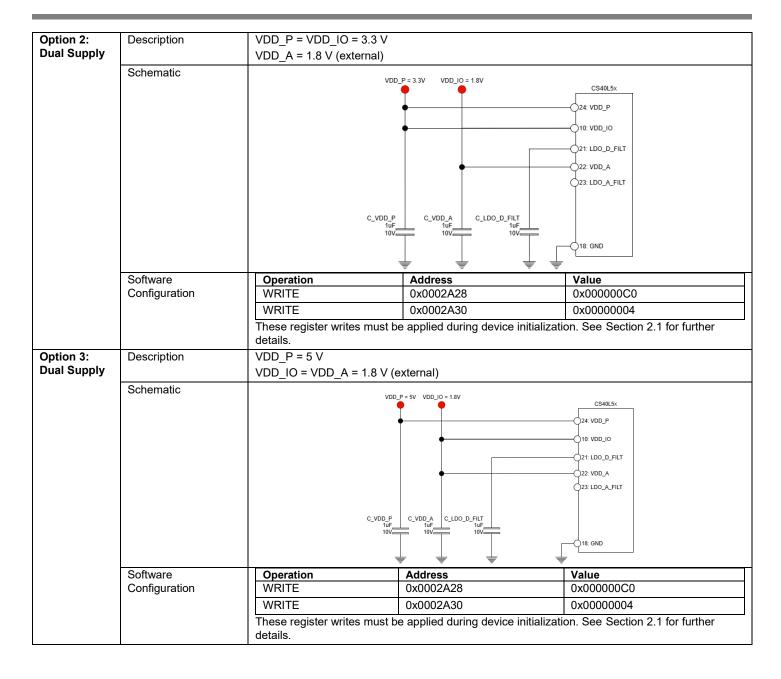

### 1.1.2 High Power Rail: Amplifier Supply

The Class D amplifier on CS40L5x can be powered internally through the boost converter, or else can be powered using an external supply. When powered internally, an external inductor (connected across VDD\_B and BST\_SW) forms part of the boost-converter circuit which supplies VDD\_AMP. The internal boost supply supports Class-H tracking, which improves the amplifier efficiency; if an external VDD\_AMP supply is used, the boost converter is bypassed.

The selection of the amplifier supply is based on the available power supply on the system. The internal boost converter is recommended when the system supply voltage VDD\_B is lower. Bypassing the boost converter by using an external supply is recommended when the system supply voltage VDD\_AMP is higher, or when the output haptic effect voltage is lower than the supplied voltage.

The table below describes the recommended amplifier supply with the internal boost and external amplifier supply configurations.

| System<br>Configuration | CS40L5x High<br>Power Rail<br>Configuration                   | Notes                                                                                                                                                   | Diagram                                                                                     |

|-------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 3 V – 15 V              | Internal Boost<br>supply - Direct<br>power rail<br>connection | When VBST <= VDD_B, the boost converter is bypassed automatically. See the notes in the next table for details of the boost-converter operating states. | 3V-13.5V  OVD_B  Internal Boost Converter  OVBST  OVD_AMP  Class D Amplifier OUTN  Actuator |

| 10 V – 15 V             | External supply -<br>Direct battery<br>connection             | Boost converter is disabled and bypassed                                                                                                                | CS40L5x  VDD_B                                                                              |

The following table shows the recommended external components for internal/external amplifier supply configurations. The component ratings shown are typical. For further details and considerations of the external components, see the schematic and layout guidelines.

Note - Refer to the CS40L5x errata for additional configuration that may be revision-dependent.

#### **MCU Driver Reference**

File: ../cs40l5x/cs40l5x.c

Function: cs40l5x\_initialize()

- Internal boost supply haptic\_config.is\_ext\_bst = false

- External supply haptic\_config.is\_ext\_bst = true

### 1.2 Operational States

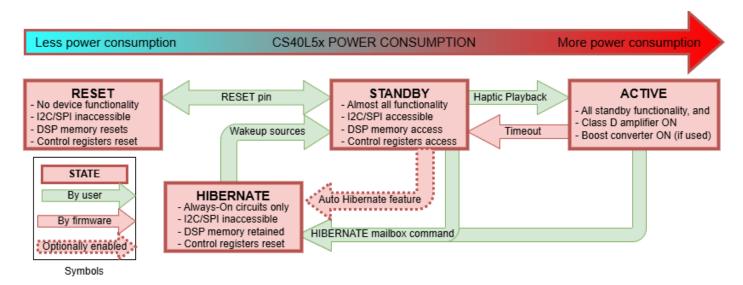

The CS40L5x supports four operational states—Reset, Standby, Active, and Hibernate. The device transitions between these states to reduce power consumption, depending on the required functionality. The diagram below shows the state transitions, based on user inputs and firmware commands.

Figure 2 Operational States

#### **MCU Driver Reference**

...cs40l5x/cs40l5x.c

Function cs40l5x power() manages the power management transitions

#### 1.2.1 Reset State

The Reset State is the lowest power state and does not support any device functionality.

CS40L5x enters the RESET state when the RESET pin is driven low, or when power is not present. When the RESET pin is set high, the device transitions to Standby State.

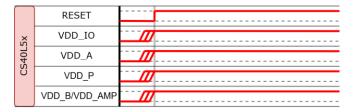

Note - The CS40L5x does not have a power-supply sequence requirements, but all power supplies must be stable prior to release of the RESET pin.

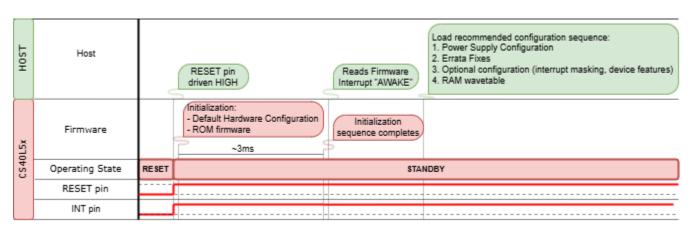

The power-supply and reset timing is illustrated in the following figure.

Figure 3 Power-On Reset Timing

#### 1.2.2 Hibernate State

The Hibernate State is a low-power state that supports a minimal always-on capability while being ready to resume operation following a valid wake-up event. Almost all device functionality is disabled in the Hibernate State; only the always-on digital functions associated with wake-up are maintained. The Hibernate State provides power consumption savings when most of the device functionality is not required, but also introduces additional latency on haptic-effect triggers due to the wake-up time.

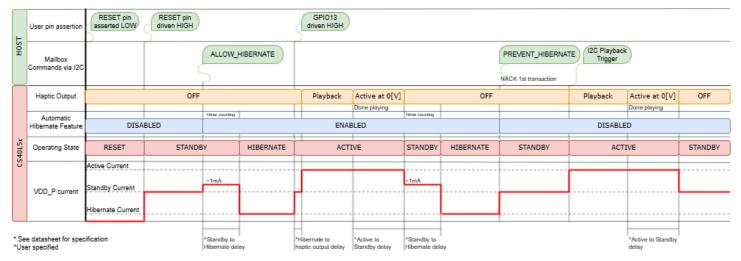

The device enters the Hibernate state when commanded via the mailbox. The device supports an optional Automatic Hibernate feature, which is enabled through the ALLOW\_HIBERNATE command. The Automatic Hibernate allows the device to select the Hibernate State automatically using a timeout following any haptic output. See Section 1.2.5 below.

| Mailbox command | Description                                                                                                                                                                                               |                                                                                      | Register v                                                         | write sequence         |                                                                                                           |                                                                      |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| HIBERNATE       | The device enters the                                                                                                                                                                                     | HIBERNATE command:                                                                   |                                                                    |                        |                                                                                                           |                                                                      |

|                 | hibernate state                                                                                                                                                                                           | Register Name                                                                        | Regist                                                             | er Address             | Data                                                                                                      |                                                                      |

|                 | immediately, even if a haptic effect is playing.                                                                                                                                                          | DSP VIRTUAL1 MBOX                                                                    | 1 0x0011                                                           | 020                    | 0x02000001                                                                                                |                                                                      |

| ALLOW_HIBERNATE | The device enters the                                                                                                                                                                                     | ALLOW HIBERNATE comm                                                                 | and                                                                |                        |                                                                                                           |                                                                      |

| _               | hibernate state after a                                                                                                                                                                                   | Register Name                                                                        | Regist                                                             | er Address             | Data                                                                                                      |                                                                      |

|                 | user-set timeout. The default timeout is 4.88                                                                                                                                                             | DSP VIRTUAL1 MBOX                                                                    | 1 0x0011                                                           | 020                    | 0x02000004                                                                                                |                                                                      |

|                 | This command enables the timer "Standby to Hibernate Timeout", which is started every time the device enters the Standby State. The PREVENT_HIBERNA TE command (see Section 1.2.2.1) disables this timer. | appended 24-bit words. The table below shows the Register Name                       |                                                                    |                        |                                                                                                           |                                                                      |

|                 |                                                                                                                                                                                                           | started every time the<br>device enters the<br>Standby State. The<br>PREVENT_HIBERNA | PM_TIMER_TIMEOUT<br>_TICKS3_LSW<br>PM_TIMER_TIMEOUT<br>_TICKS3_MSW | 0x2803FF0<br>0x2803FF4 | 0x00027100<br>0x00000000                                                                                  | Value = append MSW[23:0]:LSW[23:0] Encoding: Value = Seconds * 32768 |

|                 |                                                                                                                                                                                                           |                                                                                      |                                                                    |                        | Example: $1.22s \rightarrow 0x9C29$ Decoding: Seconds = Value/32768  Example: $0x9C29 \rightarrow 1.22 s$ |                                                                      |

Note - If Automatic Hibernate mode is enabled, the current consumption in the Standby State is increased from its typical value (~195  $\mu$ A) to approximately 1 mA while the Standby-to-Hibernate timer is active. When the timer expires, the device transitions to the Hibernate State and the current decreases to ~11  $\mu$ A. While the device is in the Hibernate State, any I2C/SPI transaction will wake up the device and restart the timer. See diagrams in Section 1.2.5.

### 1.2.2.1 Wakeup Sources

The CS40L5x device remains in the Hibernate State until a wakeup source is triggered as described in the table below.

| Wakeup source                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                        | Us                                                                                     | er interaction:     |                  |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|------------------|

| I2C/SPI transaction with address detection                                                  | Any I2C/SPI transaction targeted to the device's address wakes up the device.                                                                                                                                                                                                                                                                                                                      | Any I2C/SPI transaction (REA address. Transactions on the address do not wake up the d | same I2C/SPI bus t  |                  |

| PREVENT_HIBERNATE                                                                           | The device enters the STANDBY                                                                                                                                                                                                                                                                                                                                                                      | PREVENT_HIBERNATE com                                                                  | mand                |                  |

| mailbox command                                                                             | state immediately and disables the ALLOW_HIBERNATE timer function.                                                                                                                                                                                                                                                                                                                                 | Register Name                                                                          | Register<br>Address | Register<br>Data |

|                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                    | DSP_VIRTUAL1_MBOX_1                                                                    | 0x0011020           | 0x02000003       |

| GPIO trigger: GPIO11 GPIO12 GPIO13 Refer to Section 3.2.2 for specific waveform assignments | If GPIO11, GPIO12, or GPIO13 is assigned to trigger a haptic effect (see Section 3.2.2), the device wakes when a valid edge is detected on the respective GPIO pin.  Note that once triggered, the device transitions to active state to play the assigned waveform, and returns to standby. The device remains in the Standby State, unless the ALLOW_HIBERNATE command has been sent previously. |                                                                                        |                     |                  |

Note - The first I2C/SPI transaction received while the device is in the Hibernate State wakes the device but is not acknowledged (NACK). Therefore, the host must retransmit the I2C/SPI command once the device has completed the wake-up transition (Hibernate to Standby).

### 1.2.3 Standby State

The Standby State is a low-power state that supports control-register access using the I2C or SPI interfaces. Read/write access to the DSP memory is also supported. The device enters the Standby State in the following conditions:

- The device is in the Reset State and the RESET pin is driven high

- The device is in the Hibernate State and a wake-up source is triggered

- The device is in the Active State, has completed playing a haptic effect, and the Active-to-Standby timer has expired

#### 1.2.4 Active State

When the device is in Active State, all functional blocks are supported. Note that the boost converter, Class D amplifier, ASP interface, and other functions required for haptic output are only supported in the Active State. The device transitions to Active state when playing from the ASP I2S interface, or when a haptic effect is triggered (from GPIO or I2C/SPI, see Section 3). After the device has completed playing an effect, the device enters the Standby State after the Active-to-Standby user-configurable timer expires.

The Active to Standby timer delay PM\_PM\_TIMER\_TIMEOUT\_TICKS4 is stored in the two appended 24-bit words. This appended value is the delay in units of 1/32768 seconds. The table below shows the default values for a 244 ms delay.

| Register Name                  | Register Address | Default Data | Register Data                                      |

|--------------------------------|------------------|--------------|----------------------------------------------------|

| PM_PM_TIMER_TIMEOUT_TICKS4_LSW | 0x2803FF8        | 0x00001F40   | Value = append MSW[23:0]:LSW[23:0]                 |

| PM_PM_TIMER_TIMEOUT_TICKS4_MSW | 0x2803FFC        | 0x00000000   | Encoding:                                          |

|                                |                  |              | Value = Seconds * 32768<br>Example: 1.22s → 0x9C29 |

|                                |                  |              | Decoding:                                          |

|                                |                  |              | Seconds = Value/32768<br>Example: 0x9C29 → 1.22 s  |

## 1.2.5 Operating State Transition examples

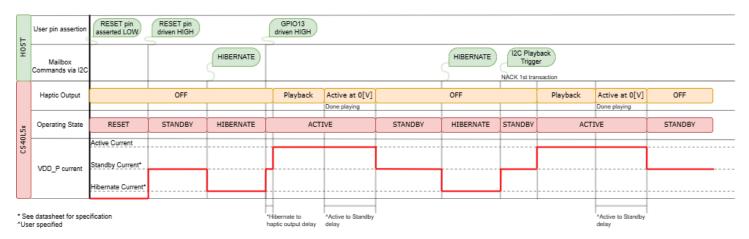

Example state transitions - without the hibernation timer enabled - are illustrated in the following figure.

Figure 4 Operating State Transitions with Automatic Hibernate Disabled

Example state transitions - without the hibernation timer enabled - are illustrated in the following figure.

Figure 5 Operating State Transitions with Automatic Hibernate Enabled

### 2 Firmware

### 2.1 Initialization Sequence

When the CS40L5x transitions from the Reset State to the Standby State, the CS40L5x is initialized with default hardware configurations, and the ROM firmware is initialized with default firmware configurations. The initialization sequence duration is typically about 3 ms.

Once CS40L5x indicates the default initialization sequence is done through the <u>Firmware Interrupt</u> "AWAKE", the user can proceed loading its configuration sequence. The following configuration sequence is recommended: 1) <u>power supply configurations</u>, 2) errata fixes, 3) other configurations such as <u>interrupt</u> and <u>device features</u> and 4) <u>RAM wavetable</u> loading.

Figure 6 Device Initialization Sequence

### 2.1.1 ROM Firmware

The CS40L5x ROM firmware contains featured algorithms including <u>Calibration</u>, <u>Click Compensation</u>, <u>Dynamic F0</u>, and Run Time Haptics. It also contains predefined ROM waveforms, which are described in detail in Section 3.1.1.

#### 2.1.2 RAM Firmware

CS40L5x RAM firmware may be developed to support new features, bug fixes, and patches. The CS40L5x ROM firmware is loaded automatically after a hardware reset; RAM firmware needs to be downloaded by the host processor after a hardware reset. The CS40L5x provides up to 24 kB memory available for a RAM firmware; the host system must provide sufficient memory storage for RAM firmware if needed. The CS40L51/52/53 devices support different algorithm features as described below:

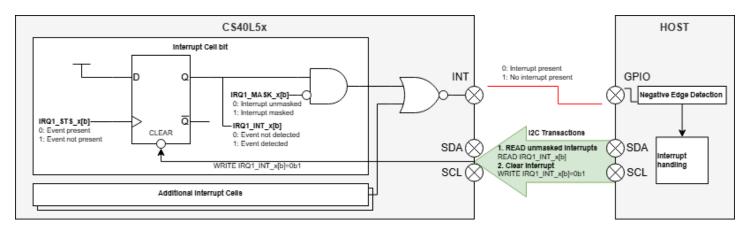

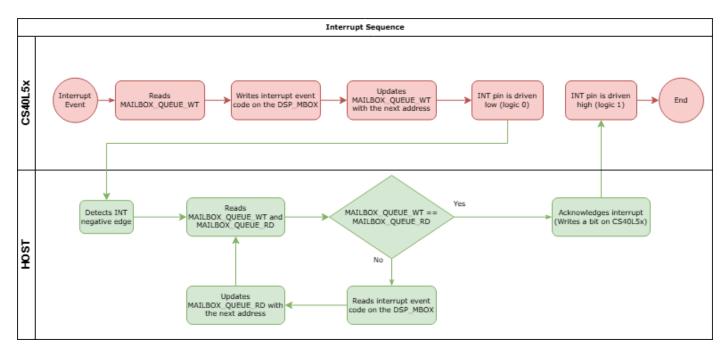

### 2.2 Interrupt

The CS40L5x device provides an interrupt pin, INT, to alert the host to significant events. The INT pin is normally high (Logic 1) and is driven low (Logic 0) when a defined interrupt event occurs. The interrupt handling by the CS40L5x and the host is illustrated in the figure below.

On CS40L5x, each bit of the IRQ1\_INT\_X registers represents an interrupt event. When an interrupt event is detected, the corresponding bit IRQ1\_INT\_X[b] is set to 1. If the interrupt is unmasked (i.e. IRQ1\_MASK\_X[b]=0), the INT pin is asserted low. Interrupt masking is handled by the host and performed at initialization. If the host detects a falling edge on the INT pin, it should read the unmasked interrupt registers bits (IRQ1\_INT\_X[b]) to determine the source of the interrupt. To clear the interrupt signal, the host must write 1 to the respective interrupt bit.

Figure 7 Interrupt Handling

The CS40L5x supports two types of interrupts: Hardware interrupts, and Firmware interrupts. Both types may trigger the INT pin when unmasked. While Hardware Interrupts are contained within interrupt cells only, Firmware Interrupts are contained on a single interrupt cell and accessed through the DSP mailbox.

Note - All hardware interrupts are masked by default. A subset of the firmware interrupts are unmasked (see Section 2.2.2 for details). The user can unmask specific interrupts by writing a 0 to the corresponding mask bit; this should be done during initialization.

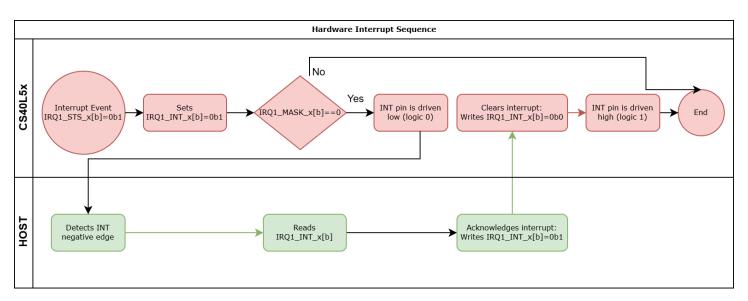

### 2.2.1 Hardware Interrupts

Hardware interrupts are handled as shown in the following figure.

Figure 8 Hardware Interrupt Sequence

The hardware interrupt registers are identified in the following table.

**Table 1 Hardware Interrupt Registers**

| Name        | Address Range           | Description                                                                                                                      | Type       |

|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| IRQ1_INT_X  | 0x0000E010 - 0x0000E058 | Each register bit indicates if an interrupt event has been detected                                                              | Read/Write |

| IRQ1_MASK_x | 0x0000E090 - 0x0000E0D8 | Each register bit indicates if an interrupt event is masked.  Note that only the unmasked interrupts trigger the INT pin output. | Read/Write |

The table below shows the most common use cases of hardware interrupts. For a complete list of interrupt event registers and the mask registers, refer to Section 7.12 in the CS40L5x datasheet.

**Table 2 Hardware Interrupt Bits**

| Register name<br>[bit] | Register Address<br>(bit) | Interrupt Name        | Description                                                                                                                                                                                             |

|------------------------|---------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ1_INT_1 [31]        | 0x0000E010 (bit 31)       | AMP_SHORT_ERR_INT1    | Amplifier short error - triggered if an overcurrent (short circuit) is detected at the amplifier output                                                                                                 |

| IRQ1_INT_8 [31]        | 0x0000E02C (bit 31)       | TEMP_ERR_INT1         | Overtemperature error - triggered if the die temperature exceeds the error threshold (~125°C)                                                                                                           |

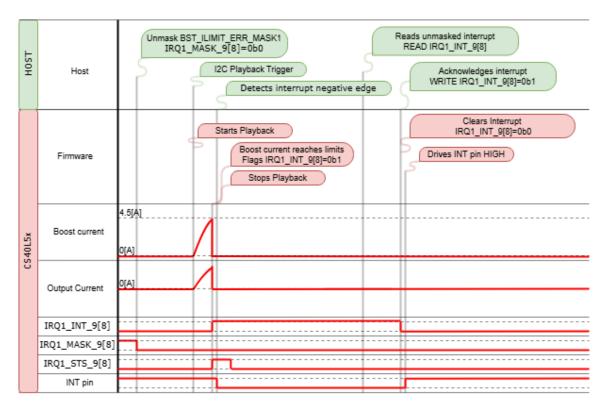

| IRQ1_INT_9 [8]         | 0x0000E030 (bit 8)        | BST_ILIMIT_ERR_INT1   | Boost current limit engagement - triggered if the average inductor current exceeds the limit threshold (~4 A) and the boost current limit is applied                                                    |

| IRQ1_INT_9 [7]         | 0x0000E030 (bit 7)        | BST_SHORT_ERR_INT1    | Boost Inductor short error - triggered if the boost overcurrent (inductor short-circuit) error is detected                                                                                              |

| IRQ1_INT_9 [6]         | 0x0000E030 (bit 6)        | BST_UVP_ERR_INT1      | Boost undervoltage error - triggered if the boost undervoltage error is detected, i.e., the output voltage (VBST) falls below the undervoltage threshold (~VDD_B x 1.1)                                 |

| IRQ1_INT_10 [16]       | 0x0000E034 (bit 16)       | UVLO_VDDBATT_ERR_INT1 | VDD_B UVLO error - triggered if VDD_B falls below the undervoltage lockout (UVLO) threshold                                                                                                             |

| IRQ1_INT_18 [15]       | 0x0000E054 (bit 15)       | GLOBAL_ERR_INT1       | Global error - triggered when there is a critical error that places the device in the Global Error State to protect the device from permanent damage - Refer to Section 4.8.5 in the CS40L5x datasheet. |

An example control sequence for a hardware interrupt is shown in the Figure below. The example assumes a haptic waveform which, if triggered, would require more current than the boost current limit. The host unmasks the boost current limit interrupt and plays the waveform. The CS40L5x attempts to generate the waveform but, when the boost current reaches its limit, the waveform playback is stopped and the INT pin is driven low (Logic 0). When the host acknowledges the interrupt, the CS40L5x clears the interrupt and drives the INT pin high (Logic 1).

Figure 9 Boost Current Limit Interrupt Example

### 2.2.2 Firmware Interrupts

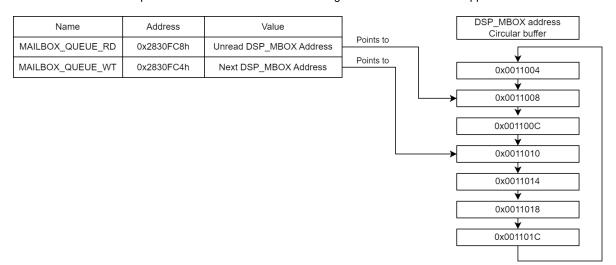

When a firmware interrupt event occurs, the event code is written into the DSP mailbox registers. The host reads the mailbox registers, updates the pointer on the device, and acknowledges the interrupt event via register write.

Figure 10 Firmware Interrupt Sequence

The following table describes the host interactions with the mailbox queue.

| Mailbox  |

|----------|

| Circular |

| Buffer   |

To find the register mailbox containing the interrupt source, the host reads the MAILBOX\_QUEUE\_RD register and updates it with the next unread address from the buffer.

| Register Name    | Address   | Range                   | Description                                | Owner   |

|------------------|-----------|-------------------------|--------------------------------------------|---------|

| MAILBOX_QUEUE_RD | 0x28042CC | 0x00011004 - 0x0001101C | Address of oldest unread element in queue. | Host    |

| MAILBOX_QUEUE_WT | 0x28042CC | 0x00011004 - 0x0001101C | Address of next empty element in queue.    | CS40L5x |

Interrupt events are stored in DSP mailbox registers in a circular buffer approach.

Note that the host should read the mailbox and update the queue pointers as fast as possible to avoid mailbox overflow (MAILBOX\_STATUS 0x2803FCC = 0x00000006).

| Interrupt |

|-----------|

| codes     |

The following interrupt codes are written to the DSP\_MBOX mailbox addresses

| Interrupt Name           | Code       | Description                                                          |

|--------------------------|------------|----------------------------------------------------------------------|

| HAPTIC_COMPLETE_MBOX     | 0x01000000 | End of haptic waveform playback from a mailbox trigger source        |

| HAPTIC_COMPLETE_GPIO     | 0x01000001 | End of haptic waveform playback from a GPI trigger source            |

| HAPTIC_TRIGGER_MBOX      | 0x01000010 | Start of a mailbox playback                                          |

| HAPTIC_TRIGGER_GPIO      | 0x01000011 | Start of a GPI playback                                              |

| INIT                     | 0x02000000 | Device transitions from reset to standby                             |

| AWAKE                    | 0x02000002 | Device transitions from hibernate to standby                         |

| PERMANENT_SHORT_DETECTED | 0x0C000C1C | A short circuit was detected at the amplifier output before playback |

| RUNTIME_SHORT_DETECTED   | 0x0C000C1D | A short circuit was detected at the amplifier output during playback |

Note that interrupt codes not listed in the table above are reserved. Contact your Cirrus Logic representative for more information.

# Acknowledge (by Host)

To acknowledge the interrupt, the host writes a 0b1 to DSP\_VIRTUAL2\_MBOX\_WR\_INT1. Then, CS40L5x drives the interrupt pin high (logic 1)

| Name       | Address   | Value      | Notes                                                  |

|------------|-----------|------------|--------------------------------------------------------|

| IRQ1_INT_2 | 0x000E014 | 0x00200000 | Write 0b1 to DSP_VIRTUAL2_MBOX_WR_INT1 (IRQ_INT_2[21]) |

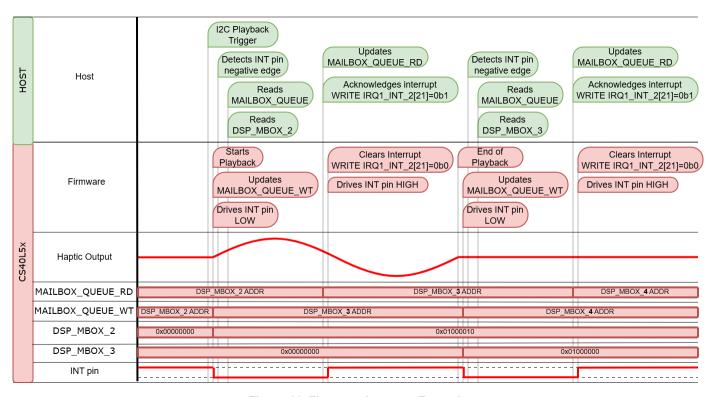

An example control sequence for a firmware interrupt is shown in the figure below.

Figure 11 Firmware Interrupt Example

# 3 Haptic Playback

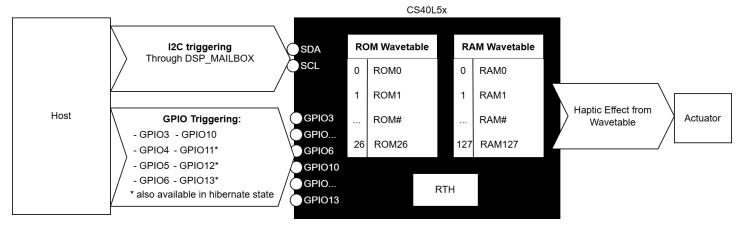

Haptic effects are stored in CS40L5x in wavetables. These effects can be triggered from GPIO or I2C/SPI mailbox commands.

Figure 12 Haptic Playback

# 3.1 Haptic Wavetables

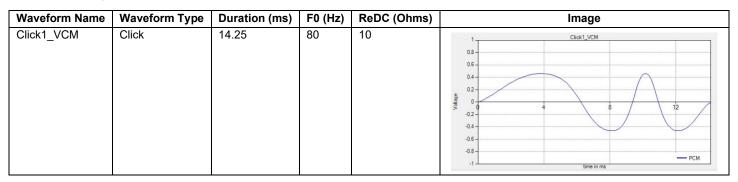

Haptic effects stored in wavetables are indexed in the formats shown in the table below. These effects are developed using the SCS software haptic-control utility.

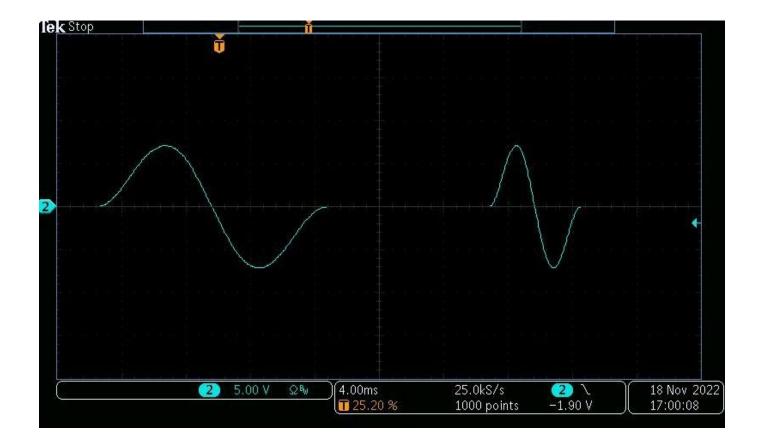

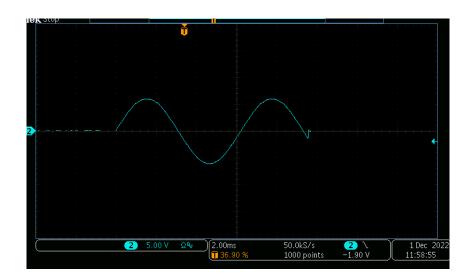

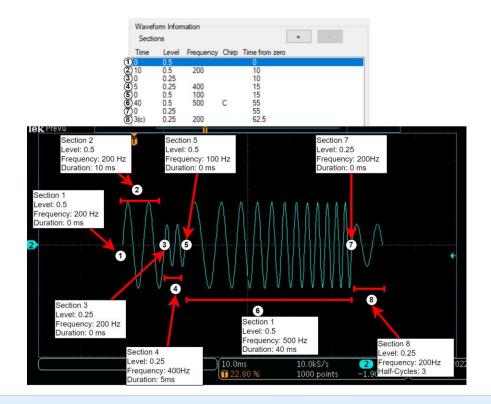

| Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Example                                                                                                                                                                                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM      | A PCM waveform specifies the instantaneous voltage over time as a pulse-code modulated (PCM) signal. These waveforms are useful for clicks, and for other short, finely tuned effects.  User defined parameters (optional, not required): F0: Resonant frequency ReDC: Actuator resistance                                                                                                                                                                                                                            | Example 160 Hz PCM:  lek Stop  2 2.50 V QN (4.00ms 25.0kS/s 2 N 18 Nov 2022 15:51:29                                                                                                                                                                                                       |

| PWLE     | A piecewise linear envelope (PWLE) specifies the amplitude envelope of a variable-frequency sine wave over time. These waveforms are useful for long-duration, low-resolution effects, such as buzzes. They are composed of sections in which the following parameters are specified:  Level (Full Scale)  Duration (ms)  Frequency (Hz)  Notes:  For section 1, only the level is user defined. The duration of section 1 is always 0.  A section of duration 0 is required when changing the level instantaneously. | PWLE defined in SCS:    Waveform Information   Section Section 2   Level: 0.25   20   0.3599   10   10   10   10   10   10   10                                                                                                                                                            |

| Ringtone | Ringtones are specified as a series of PCM / PWLE effects to play in series, with inserted delays, and changes of amplitude as needed. These waveforms are useful for creating long effects which combine or repeat other effects.                                                                                                                                                                                                                                                                                    | Ringtone using PilotTone1_160Hz as index 1 and PWLE above as index 2  **Waveform Information**  **Preparation Regions**    Part   PilotTone1_160Hz   PVLE   PVLE   PVLE   Ampilitude factor: 100    Regions**   PolotTone1_160Hz   PVLE   Ampilitude factor: 100    Ampilitude factor: 100 |

CS4045x supports playback from predefined waveforms stored in ROM. Additionally, the application-specific waveforms can be created and loaded into the RAM wavetable. Runtime Haptics (RTH) also allows the playback of effects with parameters specified by the user.

#### 3.1.1 ROM Waveform

The ROM waveform below can be used to verify software and hardware functionality during development. To trigger the ROM waveform, see Section 3.2.

### 3.1.2 RAM Wavetable

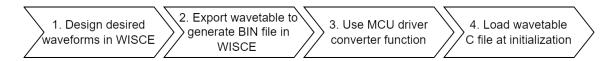

The RAM wavetable allows users to load applications-specific waveforms during CS40L5x initialization, to be used at a later time. The CS40L5x device has 11,994 bytes available to store these waveforms in RAM. Note that each RAM waveform contains a waveform header (15 bytes) and waveform data.

The user can create waveforms (PCM, PWLE and Ringtone) and store them as a wavetable .bin file using the Cirrus Logic SCS Tool. This wavetable bin is converted to .c/.h files using the firmware\_converter.py tool in the Cirrus Logic MCU Driver code to be included in the user's MCU code.

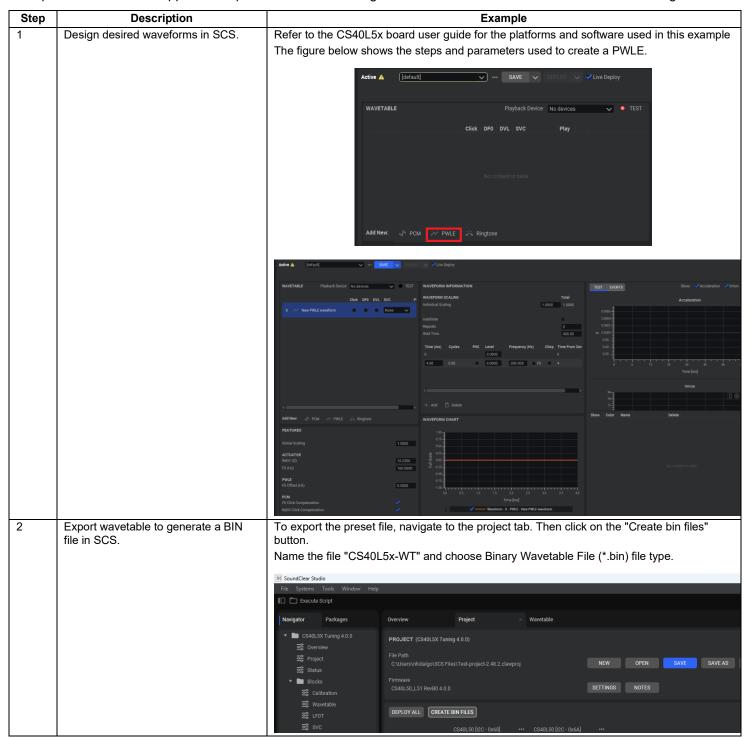

The procedure to create application-specific waveforms using the SCS software tool is described in the following table.

| Step | Description                                                                           | Example                                                                                                                                                                                                                                                                                  |

|------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | Refer to the MCU Driver Quick Start<br>Guide to obtain the Firmware                   | Run the firmware_converter.py tool from the Windows PowerShell                                                                                                                                                                                                                           |

|      | Converter Tool. This tool creates .c and .h files.                                    | PS C:\MCU-Drivers\tools\firmware_converter> python.exe .\firmware_converter.py fw_img_v1 cs40l52 ROMwmdr .\CS40L52-WT.binwmdr-only firmware_converter                                                                                                                                    |

|      | Save the Wavetable BIN file in the same directory as the firmware                     | Convert from WMFW/WMDR ("BIN") Files to C Header/Source<br>SDK version 4.27.2 - d20lcdaf89044f2Sbe78a00605a197f376226234                                                                                                                                                                 |

|      | converter and run the firmware converter tool                                         | Command: fw_img_v1 Part Number: cs40152 WMFW Path: ROM                                                                                                                                                                                                                                   |

|      | MCU Driver Reference File path:\tools\firmware_co nverter File: firmware_converter.py | \text{WMDR Path: \CSU40.52-\text{WI.bin}} \text{No suffix} \text{Input Symbol ID Header: None} \text{Generated Symbol ID Header cs40152_sym.h} \text{Exported to files:} \text{cs40152_fw_img.h} \text{cs40152_fw_img.c} \text{Exit.} \text{PS C:\MCU-Drivers\tools\firmware_converter>} |

| 4    | Include the newly created "cs40l5x_fw_img.c", "cs40l5x_fw_img.h" and                  | The "makefile" script on the MCU driver sample application runs the firmware_converter.py and includes the .c and .h files on the initialization sequence. Refer to the MCU Driver Quick Start Guide for more details.                                                                   |

|      | "cs40l5x_sym.h" to the project.                                                       | MCU Driver Reference File path:\cs40l5x File: bsp_cs40l5x.c Function: bsp_dut_boot(void)                                                                                                                                                                                                 |

| 5    | Play the RAM waveform via MAILBOX. Refer to Section 3.2.1 for details.                | Operation         Register Name         Address         Value         Notes           WRITE         DSP_VIRTUAL1_MBOX_1         0x0011020         0x01000001         Play RAM waveform index 1                                                                                           |

|      |                                                                                       | <b>2</b> 2.50 V ♀ 2.00ms 50.0kS/s 2 \ 15 Nov 2022 18:36:47                                                                                                                                                                                                                               |

# 3.1.3 Runtime Haptics Waveforms

The RAM and ROM waveforms must be defined and loaded at initialization. Runtime Haptics (RTH) waveforms can be created, loaded and played at runtime. Refer to Section 4.4 for details.

# 3.2 Triggering Options

There are two ways to trigger a haptic effect on CS40L5x - via I2C/SPI mailbox trigger and GPI triggering.

### 3.2.1 I<sup>2</sup>C/SPI Mailbox Trigger

To trigger a haptic effect from an I2C/SPI transaction, the corresponding mailbox command and wavetable index are written to the mailbox inbound address 0x0011020.

| Mailbox<br>Command | Value        | Function                                             | · ·               | Example               |  |  |  |  |  |  |  |  |

|--------------------|--------------|------------------------------------------------------|-------------------|-----------------------|--|--|--|--|--|--|--|--|

| ROM                | 0x0180000A   | ROM waveform playback.                               | Example 1: Play F | ROM waveform          |  |  |  |  |  |  |  |  |

| WAVEFORM           |              |                                                      | Address           | Value                 |  |  |  |  |  |  |  |  |

|                    |              |                                                      | 0x0011020         | 0x0180000A            |  |  |  |  |  |  |  |  |

| RAM                | 0x01000000 - | RAM wavetable playback. The last 2 digits            | Example 1: Play F | RAM15 waveform (0x0F) |  |  |  |  |  |  |  |  |

| WAVEFORM           | 0x0100007F   | correspond to the RAM wavetable index.               | Address           | Value                 |  |  |  |  |  |  |  |  |

|                    |              |                                                      | 0x0011020         | 0x0100000F            |  |  |  |  |  |  |  |  |

|                    |              |                                                      | Example 2: Play F | RAM35 waveform (0x23) |  |  |  |  |  |  |  |  |

|                    |              |                                                      | Address           | Value                 |  |  |  |  |  |  |  |  |

|                    |              |                                                      | 0x0011020         | 0x01000023            |  |  |  |  |  |  |  |  |

| RTH                | 0x01400000 - | RTH wavetable playback. The last digit corresponds   | Example 1: Play F | RTH0 waveform (0x00)  |  |  |  |  |  |  |  |  |

| WAVEFORM           | 0x01400001   | to the RTH wavetable index. There are only 2 indexes | Address           | Value                 |  |  |  |  |  |  |  |  |

|                    |              | supported in RTH wavetable (index 0 and 1).          | 0x0011020         | 0x01400000            |  |  |  |  |  |  |  |  |

|                    |              |                                                      | Example 2: Play F | RTH1 waveform (0x01)  |  |  |  |  |  |  |  |  |

|                    |              |                                                      | Address           | Value                 |  |  |  |  |  |  |  |  |

|                    |              |                                                      | 0x0011020         | 0x01400001            |  |  |  |  |  |  |  |  |

#### **MCU Driver Reference**

**File**: .../cs40l5x/cs40l5x.c

Function: cs40l5x\_trigger()

### 3.2.2 GPI Trigger

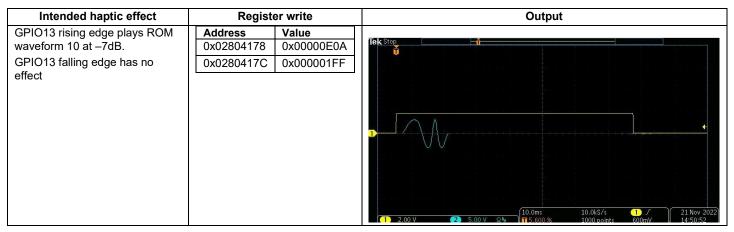

A GPIO rising or falling edge can be configured to trigger haptic effects from ROM wavetable, RAM wavetable or Runtime Haptics (RTH) waveforms. This configuration is stored in GPIO event registers and can be changed after reset.

The GPIO Event register format is defined as follows:

| Bit         | 23  | 22     | 21     | 20  | 19 | 18 | 17 | 16                                    | 15  | 14   | 13     | 12  | 11                          | 10                                                                    | 9 | 8                                                                     | 7         | 6           |     | 5  | 4 | 3  | 3 2               | 2 | 1 | 0 |

|-------------|-----|--------|--------|-----|----|----|----|---------------------------------------|-----|------|--------|-----|-----------------------------|-----------------------------------------------------------------------|---|-----------------------------------------------------------------------|-----------|-------------|-----|----|---|----|-------------------|---|---|---|

| Description | Res | served | )x0) b | 00) |    |    |    | RTH<br>Waveform<br>0=ROM/RAM<br>1=RTH | Res | erve | )x0) b | 00) | 0 = 1 = 2 = 3 = 4 = 5 = 6 = | enuati<br>0dB<br>-1dB<br>-2dB<br>-3dB<br>-4dB<br>-5dB<br>-6dB<br>-7dB |   | ROM/RAM<br>TABLE<br>0=ROM<br>1=RAM<br>(Ignored<br>for RTH<br>effects) | 0x<br>Ind | :00-<br>dex | -0x | ۲F |   | Wa | EX<br>ovefo<br>Wa |   | - | า |

Note - Setting a GPIO Event register to 0x000001FF disables the corresponding GPIO edge as a source of haptic effect triggering. Specifically for GPIO11-GPIO13, disabling a haptic effect also disables the GPI triggers as wakeup sources after the next hibernate-wake cycle.

An example configuration for GPIO13 is described below.

# 4 Device Features (Algorithms)

CS40L5x is haptic amplifier that supports waveform playback and also integrates advanced algorithms and features to improve the user experience. The <u>Click Compensation</u> feature enables stronger haptic effects, modifying the nominal parameters of a designed waveform (such as the resonance frequency, F0, and actuator resistance, ReDC,) to compensate for actuator variations arising from changes in temperature, voltage, and manufacturing tolerances. Part-to-part parameters are estimated through algorithms such as <u>Calibration</u>, which happens at the production line. The <u>Dynamic</u> F0 algorithm allows for temperature and voltage variations by estimating F0 every time a waveform is played.

| Feature                        | Description                                                                                                     | CS40L51                | CS40L52        | CS40L53 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|----------------|---------|

| Calibration (Re and F0)        | Algorithm that allows measurement of the haptic actuator electrical parameters like Fo and Re.                  | Yes                    | Yes            | Yes     |

| Click compensation (Re and F0) | Algorithm that automatically adjusts the click waveform performance to compensate for changes in the Re and F0. | Yes                    | Yes            | Yes     |

| Haptics synthesizer            | Haptics playback engine that enables generation of haptics effects.                                             | Yes                    | Yes            | Yes     |

| Runtime haptics (RTH)          | Dynamic haptic waveform generation with minimized delays.                                                       | Yes                    | Yes            | Yes     |

| Load diagnostics               | Algorithm that allows to check the status of the load connected to the output of the haptics amplifier.         | Yes                    | Yes            | _       |

| Closed-loop algorithms (SVC)   | Algorithm that enables direct control of the actuator back EMF/acceleration in real-time.                       | Yes                    | Yes            | _       |

| Audio to haptics (A2H)         | Algorithm that automatically generate haptics effects from input audio content.                                 | Yes                    |                | _       |

| Live F0 tracking (LF0T)        | Realtime resonance frequency tracking and playback.                                                             | Yes                    | _              | _       |

| Active vibration compensation  | Algorithm that actively compensates for external vibration conditions by adjusting the haptics effect playback. | Yes                    | <u> </u>       | _       |

| Wavetable sample rate          | Sample rate supported for PCM waveforms in the wavetable.                                                       | 8kHz, 24 kHz,<br>48kHz | 8kHz,<br>24kHz | 8kHz    |

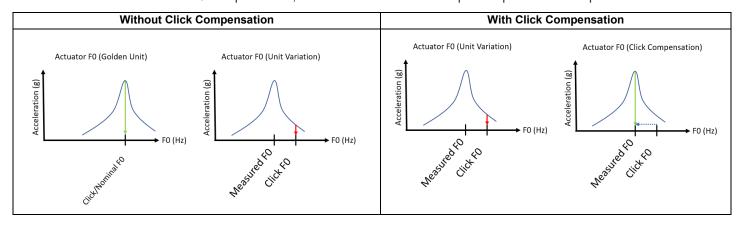

### 4.1 Click Compensation

When a waveform is designed for an actuator, it is designed with the nominal resonant frequency (F0) of the actuator in mind. This results in haptic effects that work well when the F0 of the actuator is close to the nominal F0. However, either due to manufacturing tolerance, or temperature, the actuator F0 might be far enough away from the nominal F0 to cause ringing or loss in acceleration strength. As the actuator F0 moves away from the designed click F0, acceleration strength and braking performance is lost. The CS40L5x Click Compensation feature accounts for this shift by modifying the waveform by a factor that depends on the calibrated F0 and ReDC, and the nominal F0 and ReDC of the waveform. The user can expect a stronger haptic effect when F0 compensation is enabled. The ReDC compensation produces a less noticable user effect than the F0 compensation, but is recommended for improved power consumption.

Click compensation is calculated by taking the following ratios:

$$Frequency_{factor} = \frac{VIBEGEN_FO_OTP\_STORED}{FO\_WAVEFORM}$$

$$Amplitude_{factor} = \frac{VIBEGEN\_REDC\_OTP\_STORED}{REDC\_WAVEFORM}$$

#### Where:

- VIBEGEN\_F0\_OTP\_STORED is the nominal F0 of the actuator stored in CS40L5x. This value can be obtained from F0 estimation in <u>Calibration</u>, or manually set by the user

- F0 WAVEFORM is the nominal F0 of the particular waveform

- VIBEGEN\_REDC\_OTP\_STORED is the nominal ReDC of the actuator stored in CS40L5x. This value can be

obtained from ReDC estimation in <u>Calibration</u>, or manually set by the user

- REDC WAVEFORM is the nominal ReDC of the particular waveform

The table below shows the format for the VIBEGEN\_x\_OTP\_STORED fields.

| Name                    | Address (may<br>change if a<br>RAM FW is<br>used) | Default<br>Value | Description                                                                                                                                                           |

|-------------------------|---------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIBEGEN_F0_OTP_STORED   | 0x2805C00                                         | 0x003C0000       | Format: Q10.14                                                                                                                                                        |

|                         |                                                   |                  | Default: 240Hz                                                                                                                                                        |

|                         |                                                   |                  | When Dynamic F0 is enabled, the estimated Dynamic F0 value will be used for Click Compensation and the VIBEGEN_F0_OTP_STORED is ignored. See Section 4.3 for details. |

| VIBEGEN_REDC_OTP_STORED | 0x2805C04                                         | 0x0001D000       | Format: Q7.17                                                                                                                                                         |

|                         |                                                   |                  | $\frac{(Ohms)(2.9)}{24} = Value$                                                                                                                                      |

|                         |                                                   |                  | Default: 7.50hms                                                                                                                                                      |

|                         |                                                   |                  | <b>Example</b> : 40hms → 0x0000F776                                                                                                                                   |

The waveform F0 and ReDC parameters are set depending on which wavetable the waveform belongs:

- ROM wavetable: F0 and ReDC are fixed. See Section 3.1.1.

- RAM wavetable: F0 and ReDC are defined by the user when designing the waveforms through SCS. See Section 3.1.2 for details.

- RTH waveforms: F0 and ReDC are defined by the user. See Section 4.4 for more details.

Click compensation is disabled by default. Use the following register to enable Click Compensation.

| Register Name               | Register Address | Default Value | Notes                                              |

|-----------------------------|------------------|---------------|----------------------------------------------------|

| VIBEGEN_COMPENSATION_ENABLE | 0x2805C30        | 0x00000000    | 0x00000000 = Disables Click Compensation           |

|                             |                  |               | 0x00000001 = Enables F0 Compensation only          |

|                             |                  |               | 0x00000002 = Enables ReDC Compensation only        |

|                             |                  |               | 0x00000003 = Enables both F0 and ReDC compensation |

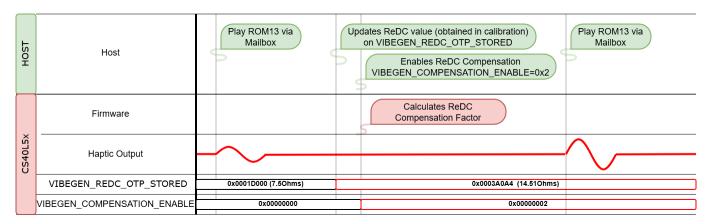

An example control sequence for ReDC compensation is shown in the Figure below. The example shows the user playing ROM13 via I2C/SPI mailbox triggering. The user then updates the ReDC value obtained earlier from calibration, enables ReDC Compensation, and plays the same click effect now with compensation. Note that the REDC\_WAVEFORM parameter of ROM13 is stored in the ROM wavetable.

Figure 13 ReDC Compensation from Calibration

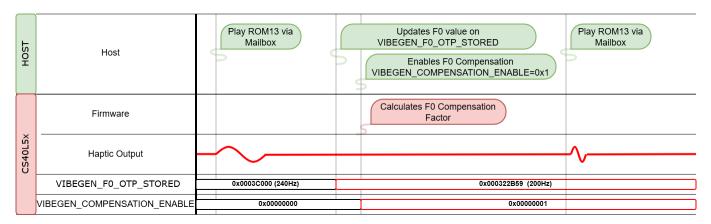

An example control sequence for F0 compensation is shown in the Figure below. The example shows the user playing ROM13 via I2C/SPI mailbox triggering. The user then updates the F0 value obtained earlier from calibration, enables F0 Compensation, and plays the same click effect now with compensation. Note that the F0\_WAVEFORM parameter of ROM13 is stored in the ROM wavetable.

Figure 14 F0 Compensation from User-Defined F0

### 4.2 Calibration

CS40L51, CS40L52, and the CS40L53 all support a calibration feature that provides the ability to track resonant frequency (F0) and resistance (ReDC) of an actuator without any external components or sensors. These parameters are measured using the integrated output voltage (VMON) and current (IMON) monitoring capabilities of CS40L5x. It is recommended to be used as part of the factory-line calibration process. The result of the calibration could be used by other algorithms that compensate for any part-to-part variation in actuator parameters.

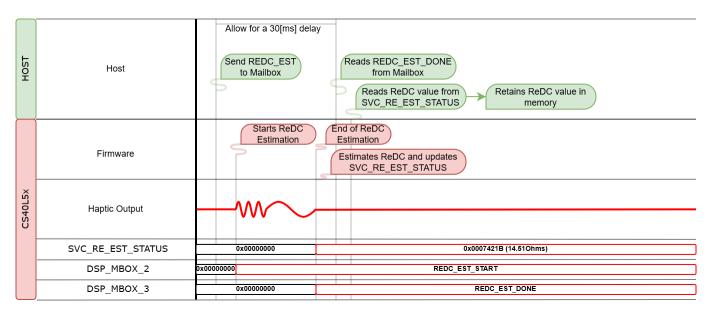

The table below describes the calibration procedure.

| Step | Description                                                |                                     |                                                                                         | Notes                                                                        | 5                           |                                                           |  |  |  |  |  |  |  |

|------|------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|

| 0    | [Optional] Set F0 estimation parameters                    | Name                                |                                                                                         | Address<br>(B0 ROM)                                                          | Default Value               | Description                                               |  |  |  |  |  |  |  |

|      | Cott o Communion parameters                                | F0_ESTIMATION_FI                    | REQ_SPAN                                                                                | 0x2802F70                                                                    | 0x00140000                  | The frequency (Hz) span of the chirp                      |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | <b>Format</b> : Q9.14                                     |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 80 Hz                                            |  |  |  |  |  |  |  |

|      |                                                            | F0_ESTIMATION_FI                    | STIMATION_FREQ_CENTRE 0x2802F74 0x003C0000 The center (Hz) of the                       |                                                                              |                             |                                                           |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Format: Q9.14                                             |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 160 Hz                                           |  |  |  |  |  |  |  |

|      |                                                            | F0_ESTIMATION_C                     | HIRP_AMP                                                                                | 0x2802F78                                                                    | 0x000CCCCD                  | The chirp amplitude (FS)                                  |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Format: Q0.23                                             |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 0.1 FS                                           |  |  |  |  |  |  |  |

|      |                                                            | F0_ESTIMATION_R                     | EDC*                                                                                    | 0x2802F7C                                                                    | 0x0003C000                  | The actuator Re DC estimate                               |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Format: Q8.15                                             |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 14.5 Ohm                                         |  |  |  |  |  |  |  |

|      |                                                            | value for F0 estimation             | n is recommend                                                                          | led. Otherwise,                                                              | the F0 estimation           | 0 estimation and copying that will use the default value. |  |  |  |  |  |  |  |

| 1    | Send calibration request to                                | Write the desired calib             | d calibration command to the DSP_VIRTUAL1_MBOX_1 register 0x001102  Command Description |                                                                              |                             |                                                           |  |  |  |  |  |  |  |

|      | DSP_VIRTUAL1_MBOX_1                                        | Name                                | Command                                                                                 |                                                                              |                             |                                                           |  |  |  |  |  |  |  |

|      |                                                            | F0_EST                              | 0x07000001                                                                              |                                                                              | F0 Estimation chir          | p                                                         |  |  |  |  |  |  |  |

|      |                                                            | REDC_EST                            | 0x07000002                                                                              | Starts the ReDC Estimation  Starts ReDC estimation first, then F0 estimation |                             |                                                           |  |  |  |  |  |  |  |

|      |                                                            | REDC_F0_EST                         | 0x07000003                                                                              |                                                                              | •                           |                                                           |  |  |  |  |  |  |  |

|      |                                                            | The CS40L5x acknow DSP_VIRTUAL1_MB0 | OX_1 0x001102                                                                           | 0 register.                                                                  |                             | tne                                                       |  |  |  |  |  |  |  |

| 2    | [Optional]                                                 | See Section 2.2.2 for o             |                                                                                         |                                                                              |                             |                                                           |  |  |  |  |  |  |  |

|      | Read calibration status (allow for a 30 millisecond delay) | Name<br>F0_EST_START                |                                                                                         | ommand<br>(07000011                                                          | Description<br>F0 Estimatio | n otostod                                                 |  |  |  |  |  |  |  |

|      | ioi a 30 millisecond delay)                                | F0_EST_START                        | -                                                                                       | (07000011                                                                    | F0 Estimatio                |                                                           |  |  |  |  |  |  |  |

|      |                                                            | REDC EST START                      |                                                                                         | (07000021                                                                    | ReDC Estim                  |                                                           |  |  |  |  |  |  |  |

|      |                                                            | REDC EST DONE                       |                                                                                         | (07000012                                                                    |                             | ation complete                                            |  |  |  |  |  |  |  |

| 3    | Read calibration results (allow                            | Calibration results are             |                                                                                         |                                                                              |                             | audit complete                                            |  |  |  |  |  |  |  |

|      | for a 30 millisecond delay)                                | Name                                | Α                                                                                       | ddress<br>30 ROM)                                                            | Default Value               | Description                                               |  |  |  |  |  |  |  |

|      |                                                            | F0 ESTIMATION F                     | Estimate of the F0                                                                      |                                                                              |                             |                                                           |  |  |  |  |  |  |  |

|      |                                                            |                                     | _                                                                                       | x24017C0                                                                     | 0x00000000                  | Format: Q9.14                                             |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 0 Hz                                             |  |  |  |  |  |  |  |

|      |                                                            | SVC_RE_EST_STA                      | TUS 0                                                                                   | x3401110                                                                     | 0x00000000                  | Estimate of the Re DC                                     |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Format: S8.15                                             |  |  |  |  |  |  |  |

|      |                                                            |                                     |                                                                                         |                                                                              |                             | Default: 0 Ohm                                            |  |  |  |  |  |  |  |

Note - Once calibration is done, the host should store the calibration values in its memory. If the user wants to use these values for click compensation, they need to be copied to the VIBEGEN\_x\_OTP\_STORED registers. See Section 4.1 for details.

An example control sequence for ReDC compensation is shown in the Figure below.

Figure 15 ReDC Calibration

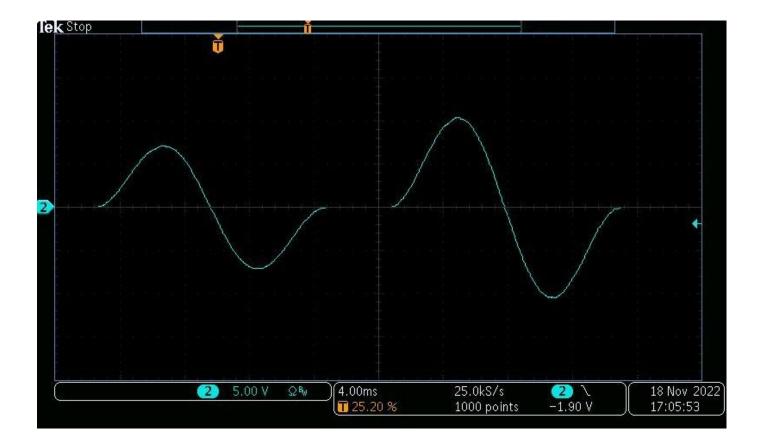

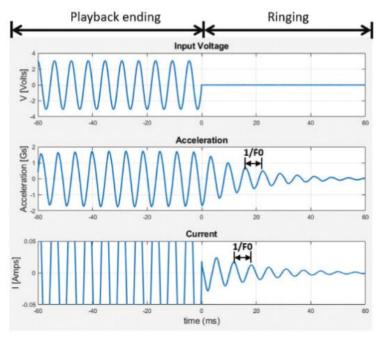

### 4.3 Dynamic F0

Dynamic F0 is an algorithm that estimates F0 after a haptic waveform playback, which could vary due to actuator manufacturing or temperature/environmental changes. This is done by the "Ring-Down" method. When the device stops driving the actuator, the mass may still be in motion, and may "ring". While the actuator is still moving, it generates back-EMF (bEMF), which is measured through VMON/IMON. The diagram below shows an example of how F0 is determined from ringing after a waveform ends playback.

Figure 16 Dynamic F0

If Dynamic F0 is enabled, the CS40L5x measures the bEMF through VMON/IMON. If the IMON peaks are above the ringing threshold, Dynamic F0 estimates and updates the F0 for that particular waveform. The table below shows the registers to enable Dynamic F0 and set the ringing threshold.

| Name                           | Address    | Default    | Description                                                                                              |

|--------------------------------|------------|------------|----------------------------------------------------------------------------------------------------------|

|                                |            | Value      |                                                                                                          |

| DYNAMIC_F0_DYNAMIC_F0_ENABLED  | 0x0280285C | 0x00000000 | 0x0 = Dynamic F0 is disabled (Default)                                                                   |

|                                |            |            | 0x1 = Dynamic F0 is enabled                                                                              |

| DYNAMIC_F0_IMONRINGPPTHRESHOLD | 0x02802860 | 0x000020C5 | Ringdown threshold factor. Dynamic F0 estimates a new F0 when the IMON measured is above this threshold. |

|                                |            |            | Format: Q1.23                                                                                            |

|                                |            |            | Default:                                                                                                 |

|                                |            |            | ROM A1: 0x00008312 → 0.004                                                                               |

|                                |            |            | ROM B0: 0x000020C5 → 0.001                                                                               |

After the dynamic F0 has been estimated for a particular waveform, the CS40L5x stores it on the Dynamic F0 table every time the waveform is played and the ringdown is above the threshold.

Note - ROM and RAM waveforms are stored and played using a wavetable index. The Dynamic F0 function supports F0 estimation for ROM and RAM waveforms, but uses the same index to store the estimated F0 for either wavetable. Therefore, Dynamic F0 should not be enabled for ROM and RAM waveforms with the same index.

Note - The Dynamic F0 algorithm only tracks F0 for the first 20 waveforms played with Dynamic F0 enabled, regardless of the number of waveforms stored in ROM or RAM with Dynamic F0 enabled.

If Click Compensation for PCM is enabled, CS40L5x uses the Dynamic F0 for the F0 compensation. Similarly for PWLEs - the CS40L5x uses the estimated Dynamic F0 when a section is set to play at F0. Otherwise, it will use the VIBEGEN\_F0\_OTP\_STORED value.

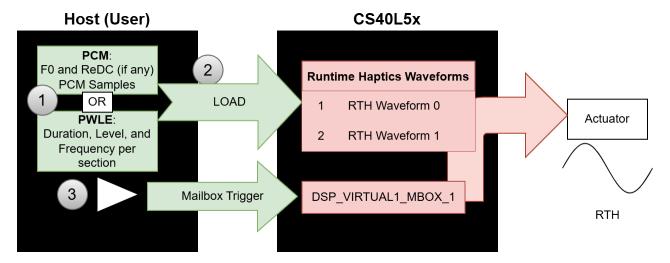

# 4.4 Runtime Haptics (RTH)

While RAM and ROM waveforms have to be predefined and loaded at initialization, Runtime Haptics (RTH) waveforms can be created, loaded and played at runtime. It currently supports Runtime Haptics PCM (RTH PCM) and Runtime Haptics Piecewise Linear Envelope (RTH PWLE) waveforms. The RTH waveforms do not need to be stored for future playback as they are dynamically defined by the user. The diagram below shows the procedure to use RTH.

Figure 17 Run-Time Haptics

- 1. Define the desired waveform following the format below.

- a. For RTH PCM, the user defines

- i. F0 and ReDC (optional)

- ii. PCM samples up to 378 (required)

- b. For RTH PWLE, the user defines

- i. Number of sections up to 63

- ii. Duration, level, and frequency of each section

- 2. Load the waveform to a RTH index address

- 3. Play the RTH waveform via I2C/SPI mailbox trigger

- 4. (Optional) Modify any of the parameters above, and repeat steps 2 and 3.

The RTH wavetable supports up to 378 samples for PCM waveforms, and up to 63 sections for PWLE waveforms.

### 4.4.1 RTH Registers

The RTH waveform registers are summarized in the following table. These registers may change in a RAM FW variant.

| Field Name            | RTH Waveform - Index 0 | RTH Waveform - Index 1 | Register Data                  |

|-----------------------|------------------------|------------------------|--------------------------------|

|                       | Register Address       | Register Address       |                                |

| RTH_WAVEFORM_TYPE     | 0x2807770              | 0x280797C              | Value :                        |

|                       |                        |                        | RTH_PCM: 0x0000_0008 (Default) |

|                       |                        |                        | RTH_PWLE: 0x0000_000C          |

|                       |                        |                        | Format: Q24.0                  |

| RTH_WAVEFORM_DATA_1   | 0x280777C              | 0x2807988              | Value:                         |

| RTH_WAVEFORM_DATA_2   | 0x2807780              | 0x280798C              | See RTH_PCM_DATA               |