# Fractional-N Clock Synthesizer and Clock Multiplier

#### **Features**

- Frequency synthesizer based on delta-sigma fractional-N analog PLL

- Generates a low-jitter 6–75 MHz clock (CLK\_OUT) from 8–75 MHz timing reference clock (REF\_CLK)

- · Clock multiplier and jitter reduction based on hybrid PLL

- Generates a low-jitter 6–75 MHz clock (CLK\_OUT) from a jittery or intermittent 50 Hz–30 MHz input clock source (CLK\_IN)

- · Highly accurate PLL multiplication factor

- Less than 1 PPM

- · I2C/SPI control port

- · Configurable auxiliary output

- · Flexible sourcing of timing reference clock

- External clock and external crystal

- Period jitter of 40 ps<sub>RMS</sub> for REF\_CLK

- Minimal board space required

- No external analog loop-filter components

- Glitchless clock outputs derived from an intermittent input clock

### **Applications**

- · Digital audio systems

- · Network and USB audio interfaces

- IoT sensor and transducer systems

- · Embedded systems

- · Automotive audio systems

Target Product Information

This document contains information for a product under development. Cirrus Logic reserves the right to modify this product.

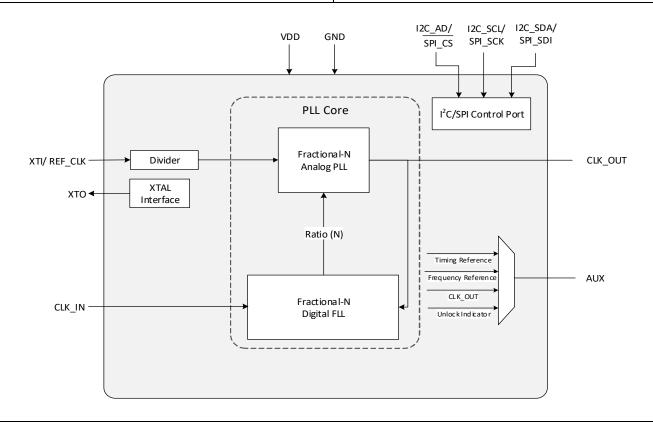

### **General Description**

The CS2500 is a system-clocking device that uses a programmable phase-locked loop (PLL). The hybrid analog/digital PLL architecture comprises a delta-sigma fractional-N analog PLL and a digital frequency-locked loop (FLL). The CS2500 enables frequency synthesis and clock generation from a stable timing reference clock. The device can generate low-jitter clocks from a noisy input clock source at frequencies as low as 50 Hz. The CS2500 can be configured using a control interface supporting I<sup>2</sup>C and SPI modes of operation.

The CS2500 can be powered from a single 1.8 V or 3.3 V supply. The device combines high performance with low power consumption.

The CS2500 is available in commercial-grade, 10-pin TSSOP package for operation from –40°C to +85°C. The device is also available in the AEC-Q100-qualified grade-2 package for operation from –40°C to +105°C.

### **Table of Contents**

| 1 Pin Assignments and Descriptions                                                                                       | 4   |

|--------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                          |     |

| 1.1 TSSOP Package Drawing (Top View, Through Package) 1.2 Pin Descriptions                                               | . 4 |

| 1.3 Electrostatic Discharge (ESD) Protection Circuitry                                                                   | . 5 |

| 2 Typical Connection Diagram                                                                                             | 6   |

| 3 Characteristics and Specifications                                                                                     | 7   |

| Table 3-1. Recommended Operating Conditions Table 3-2. Absolute Maximum Ratings Table 3-3. DC Electrical Characteristics | 7   |

| Table 3-2. Absolute Maximum Ratings                                                                                      | 7   |

| Table 3-4. AC Flectrical Characteristics                                                                                 | 7   |

| Table 3-5. Switching Specifications—I <sup>2</sup> C Control Port                                                        | ξ   |

| Table 3-6. Switching Specifications—SPI Control Port                                                                     | 1(  |

| 4 Revision History                                                                                                       | 11  |

## 1 Pin Assignments and Descriptions

These sections show pin assignments and describe pin functions.

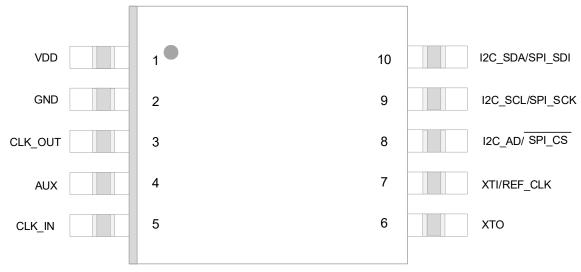

## 1.1 TSSOP Package Drawing (Top View, Through Package)

Figure 1-1. TSSOP 10-Pin Package Assignments (Top View, Through-Package)

## 1.2 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin Name        | Pin# | Power<br>Supply | I/O | Description                                                                                                                                | Internal<br>Connection | State at Reset |

|-----------------|------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|

| VDD             | 1    | _               |     | <b>Power Supply.</b> 3.3 V/1.8 V supply for the digital and analog blocks.                                                                 | _                      | _              |

| GND             | 2    | _               | _   | Ground.                                                                                                                                    | _                      | _              |

| CLK_OUT         | 3    | VDD             | 0   | Clock Output. PLL clock output.                                                                                                            | _                      | _              |

| AUX             | 4    | VDD             | 0   | Auxiliary Output. Configurable input/output clock or status output.                                                                        | _                      | _              |

| CLK_IN          | 5    | VDD             | ı   | Clock Input. Frequency reference input for the digital PLL.                                                                                | _                      | _              |

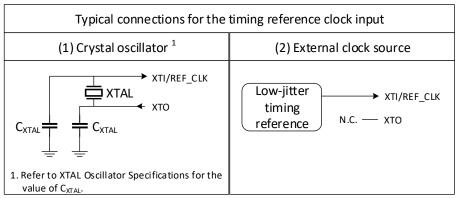

| хто             | 6    | VDD             | I/O | <b>Crystal Connection.</b> Output for an external crystal to generate the low-jitter PLL input clock.                                      | _                      | _              |

| XTI/REF_CLK     | 7    | VDD             | ı   | <b>Crystal Connection.</b> Input for an external crystal to generate the low-jitter PLL input clock.                                       | _                      | _              |

|                 |      |                 |     | <b>Reference Clock.</b> External low-jitter timing reference input clock.                                                                  |                        |                |

| I2C_AD/SPI_CS   | 8    | VDD             | I   | I <sup>2</sup> C Control-Port Address. Chip address input for the I <sup>2</sup> C interface.                                              | _                      | _              |

|                 |      |                 |     | <b>SPI Control-Port Chip Select.</b> Active-low chip select input for the SPI interface.                                                   |                        |                |

| I2C_SCL/SPI_SCK | 9    | VDD             | I   | I2C Control-Port Clock. Clock input for the I2C interface.                                                                                 | _                      | _              |

|                 |      |                 |     | SPI Control-Port Clock. Clock input for the SPI interface.                                                                                 |                        |                |

| I2C_SDA/SPI_SDI | 10   | VDD             | I/O | I <sup>2</sup> C Control-Port Data. Data input/output for the I <sup>2</sup> C interface. SPI Control-Port Serial Data In. SPI data input. | _                      | _              |

PB1034R2

## 1.3 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS2500 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is to be qualified to current JEDEC ESD standards.

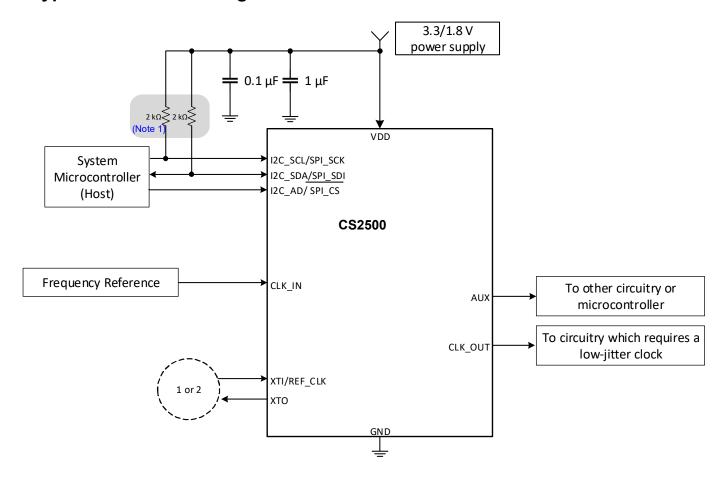

## 2 Typical Connection Diagram

Figure 2-1. Typical Connection Diagram

Notes referenced in the typical connection diagrams:

1. The pull-up resistors are required only for I<sup>2</sup>C operation.

## 3 Characteristics and Specifications

### **Table 3-1. Recommended Operating Conditions**

Test Conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground.

| Parame                       | ters                                | Symbol              | Min        | Тур | Max       | Units |

|------------------------------|-------------------------------------|---------------------|------------|-----|-----------|-------|

| DC power supply <sup>1</sup> |                                     | VDD                 | 3.1        | 3.3 | 3.5       | V     |

|                              |                                     |                     | 1.77       | 1.8 | 1.89      | V     |

| Supply ramp up/down          |                                     | t <sub>PWR-UD</sub> | 0.01       | _   | 10        | ms    |

| Ambient temperature          | Commercial Grade<br>AEC-Q100 Grade2 | / \                 | -40<br>-40 | _   | 85<br>105 | °C    |

<sup>1.</sup> The system can be either powered with a 3.3 V or a 1.8 V DC power supply.

#### Table 3-2. Absolute Maximum Ratings

Test Conditions (unless specified otherwise): Ground = GND = 0 V; voltages are with respect to ground.

| Parameters                                       | Symbol            | Min  | Max       | Units |

|--------------------------------------------------|-------------------|------|-----------|-------|

| DC power supply                                  | VDD               | -0.3 | 4.32      | V     |

| External voltage applied to digital input/output | V <sub>INDI</sub> | -0.3 | VDD + 0.3 | V     |

| Input current                                    | l <sub>in</sub>   | _    | ±10       | mA    |

| Ambient temperature                              | T <sub>A</sub>    | -55  | 125       | °C    |

| Storage temperature                              | T <sub>STG</sub>  | -65  | 150       | °C    |

#### **Table 3-3. DC Electrical Characteristics**

Test Conditions (unless specified otherwise): VDD = 3.3 V; T<sub>A</sub> = 25°C; timing reference = external REF\_CLK.

| Parameters                                   | Symbol          | Min        | Тур  | Max        | Units |

|----------------------------------------------|-----------------|------------|------|------------|-------|

| Power supply current – unloaded <sup>1</sup> | $I_{VDD}$       | _          | 3.94 | TBD        | mA    |

| Power dissipation – unloaded                 | $P_{D}$         | _          | 13   | TBD        | mW    |

| Input leakage current (per pin)              | I <sub>IN</sub> | _          | _    | ±10        | μΑ    |

| Input capacitance (per pin)                  | Ic              | _          | _    | 5          | pF    |

| High-level input voltage                     | V <sub>IH</sub> | 0.70 × VDD | _    | _          | V     |

| Low-level input voltage                      | $V_{IL}$        | _          | _    | 0.30 × VDD | V     |

| High-level output voltage                    | V <sub>OH</sub> | 0.90 × VDD | _    | _          | V     |

| Low-level output voltage                     | V <sub>OL</sub> | _          | _    | 0.10 × VDD | V     |

<sup>1.</sup>To calculate the additional current consumption due to loading (per output pin), multiply clock output frequency by load capacitance (C<sub>L</sub>) and power supply voltage (VDD).

#### **Table 3-4. AC Electrical Characteristics**

Test Conditions (unless specified otherwise): VDD = 3.3 V;  $T_A = -40 ^{\circ}\text{C}$  to  $85 ^{\circ}\text{C}$  (commercial grade);  $T_A = -40 ^{\circ}\text{C}$  to  $105 ^{\circ}\text{C}$  (AEC-Q100 grade-2); Load capacitance ( $C_L$ ) = 15 pF.

| Parameters                                 |                                                       | Symbol               | Min | Тур | Max                 | Units             |

|--------------------------------------------|-------------------------------------------------------|----------------------|-----|-----|---------------------|-------------------|

| Crystal frequency<br>Fundamental mode XTAL | RefClkDiv[1:0] = 10                                   | f <sub>XTAL</sub>    | 8   | _   | 18.75               | MHz               |

| Fundamental mode XTAL                      | RefClkDiv[1:0] = 01                                   |                      | 16  |     | 37.50               | MHz               |

|                                            | RefClkDiv[1:0] = 00                                   |                      | 32  | _   | 50                  | MHz               |

|                                            | Drive power                                           |                      | _   | _   | 100                 | μW                |

|                                            | Negative resistance                                   |                      | 500 | _   | _                   | Ω                 |

|                                            | Maximum capacitance (C <sub>XTAL</sub> ) <sup>1</sup> |                      | _   | _   | 50                  | pF                |

| Reference clock input frequency            | RefClkDiv[1:0] = 10                                   | f <sub>REF_CLK</sub> | 8   | _   | 18.75               | MHz               |

|                                            | RefClkDiv[1:0] = 01                                   | _                    | 16  |     | 37.50               | MHz               |

|                                            | RefClkDiv[1:0] = 00                                   |                      | 32  | _   | 75                  | MHz               |

| Reference clock input duty cycle           |                                                       | D <sub>REF_CLK</sub> | 45  | _   | 55                  | %                 |

| Clock input frequency                      |                                                       | f <sub>CLK_IN</sub>  | 50  | _   | 30 ×10 <sup>6</sup> | Hz                |

| Clock input pulse width <sup>2</sup>       | f <sub>CLK IN</sub> < f <sub>SYS CLK</sub> / 96       | pw <sub>CLK</sub> in | 2   | _   | _                   | UI                |

|                                            | f <sub>CLK_IN</sub> > f <sub>SYS_CLK</sub> / 96       | _                    | 10  | _   | _                   | ns                |

| PLL clock output frequency <sup>3</sup>    |                                                       | f <sub>CLK_OUT</sub> | 6   | _   | 75                  | MHz               |

| PLL clock output duty cycle                | Measured at VDD / 2                                   | t <sub>OD</sub>      | 45  | 50  | 55                  | %                 |

| Clock output rise time                     | 20% to 80% of VDD                                     | t <sub>OR</sub>      |     | 1.7 | 3.0                 | ns                |

| Clock output fall time                     | 80% to 20% of VDD                                     | t <sub>OF</sub>      |     | 1.7 | 3.0                 | ns                |

| Period jitter <sup>4</sup>                 | REF_CLK                                               | $t_{JIT}$            |     | 40  |                     | ps <sub>RMS</sub> |

PB1034R2 7

#### Table 3-4. AC Electrical Characteristics (Cont.)

Test Conditions (unless specified otherwise): VDD = 3.3 V;  $T_A = -40 ^{\circ}\text{C}$  to  $85 ^{\circ}\text{C}$  (commercial grade);  $T_A = -40 ^{\circ}\text{C}$  to  $105 ^{\circ}\text{C}$  (AEC-Q100 grade-2); Load capacitance ( $C_L$ ) = 15 pF.

| Parameters                                  |                                    | Symbol           | Min | Тур | Max   | Units             |

|---------------------------------------------|------------------------------------|------------------|-----|-----|-------|-------------------|

| Baseband TIE jitter (100 Hz to 40 kHz) 4, 5 | REF_CLK                            |                  | _   | 50  | _     | ps <sub>RMS</sub> |

| Wideband TIE jitter (100 Hz Corner) 4, 6    | REF_CLK                            | _                | _   | 165 | _     | ps <sub>RMS</sub> |

| PLL lock time – CLK_IN <sup>7</sup>         | $f_{CLK_{IN}} < 200 \text{ kHz}$   | $t_{LC}$         | _   | 100 | 200   | UI                |

|                                             | f <sub>CLK_IN</sub> > 200 kHz      |                  | _   | 1   | 3     | ms                |

| PLL lock time – REF_CLK                     | f <sub>REF_CLK</sub> = 8 to 75 MHz | t <sub>LR</sub>  | _   | 1   | 3     | ms                |

| Output frequency resolution 4, 8            | High resolution                    | F <sub>err</sub> | 0   | _   | ±0.50 | ppm               |

|                                             | High multiplication                |                  | 0   | _   | ±112  | ppm               |

| Time to first locked clock output 9         | After boot-up                      | _                | _   | _   | 20    | ms                |

| Maximum output frequency deviation 10       |                                    | _                | _   | _   | TBD   | %                 |

- 1. Refer to XTAL oscillator specifications for the value of CXTAL.

- 2.UI (unit interval) corresponds to  $t_{SYS\_CLK}$  or 1 /  $f_{SYS\_CLK}$ .

- 3.f<sub>CLK OUT</sub> = 75 MHz is ratio-limited when f<sub>CLK IN</sub> is below 72 Hz (high multiplication) or 18.3 kHz (high precision).

- 4.REF\_CLK is a 12 MHz timing reference clock. If the phase noise of REF\_CLK is 20 dB lower than the output clock's noise across the bandwidth spectrum, the clock is considered jitter-free. The clock output frequency (f<sub>CLK\_OUT</sub>) is 24.576 MHz and sample size is 10000.

- 5.3rd order 100 Hz 40 kHz bandpass filtered according to AES-12id-2020 section 3.4.2.

- 6.3rd order 100 Hz high pass filtered according to AES-12id-2020 section 3.4.1.

- 7. UI corresponds to t<sub>CLK IN</sub> or 1 / f<sub>CLK IN</sub>.

- 8. The frequency accuracy of the PLL clock output is directly proportional to the accuracy of the input clocks.

- 9. The time to first locked clock o/p is calculated for  $f_{CLK\_IN}$  = 48 kHz and lock time = 100 UI.

- 10. This parameter refers to the maximum frequency deviation in the Multiplier mode after the CLK\_IN signal is lost and before the dynamic ratio is fixed.

PB1034R2 8

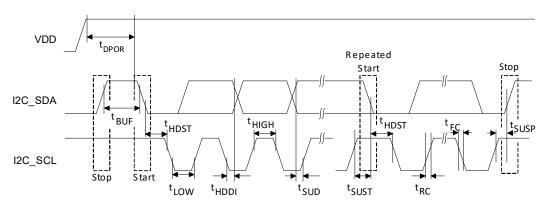

### Table 3-5. Switching Specifications—I<sup>2</sup>C Control Port

Test conditions (unless specified otherwise): VDD = 3.3 V; Ground = GND = 0 V; voltages are with respect to ground; input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds, output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds;  $T_A = 25^{\circ}C$ .

| Parameters <sup>1</sup>                                | Symbol            | Min | Max  | Units |

|--------------------------------------------------------|-------------------|-----|------|-------|

| SCL clock frequency                                    | f <sub>SCL</sub>  | _   | 100  | kHz   |

| Clock low time                                         | t <sub>LOW</sub>  | 4.7 | _    | μs    |

| Clock high time                                        | t <sub>HIGH</sub> | 4.0 | _    | μs    |

| Start condition hold time (before first pulse clock)   | t <sub>HDST</sub> | 4.0 | _    | μs    |

| Setup time for repeated start                          | t <sub>SUST</sub> | 4.7 | _    | μs    |

| Rise time of SCL and SDA                               | t <sub>RC</sub>   | _   | 1    | μs    |

| Fall time SCL and SDA                                  | t <sub>FC</sub>   | _   | 300  | ns    |

| Setup time for stop condition                          | t <sub>SUSP</sub> | 4.7 | _    | μs    |

| SDA setup time to SCL rising                           | t <sub>SUD</sub>  | 250 | _    | ns    |

| SDA input hold time from SCL falling <sup>2</sup>      | t <sub>HDDI</sub> | 0   | _    | ns    |

| Bus free time between transmissions                    | t <sub>BUF</sub>  | 4.7 | _    | μs    |

| Acknowledge delay from SCL falling                     | t <sub>ACK</sub>  | 300 | 1000 | ns    |

| Delay from supply voltage stable to control port ready | t <sub>DPOR</sub> |     | 200  | μs    |

#### 1. I<sup>2</sup>C control-port timing.{150}

2.Data must be held long enough to bridge the transition time (t<sub>FC</sub>) of SCL.

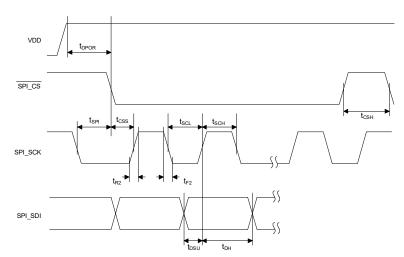

#### Table 3-6. Switching Specifications—SPI Control Port

Test conditions (unless specified otherwise): VDD = 3.3 V; Ground = GND = 0 V; voltages are with respect to ground; input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds, output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds;  $T_A = 25^{\circ}C$ .

| Parameters <sup>1</sup>                                             | Symbol            | Min | Max | Units |

|---------------------------------------------------------------------|-------------------|-----|-----|-------|

| SCK clock frequency                                                 | f <sub>SCL</sub>  | _   | 6   | MHz   |

| SCK edge to CS falling 2                                            | t <sub>SPI</sub>  | 500 | _   | ns    |

| CS high time between transmissions                                  | t <sub>CSH</sub>  | 1   | _   | μs    |

| CS falling to SCK rising edge                                       | t <sub>CSS</sub>  | 20  | _   | ns    |

| SCK pulse width low                                                 | t <sub>SCL</sub>  | 66  | _   | ns    |

| SCK pulse width high                                                | tscн              | 66  | _   | ns    |

| SDI to SCK rising setup time                                        | t <sub>DSU</sub>  | 40  | _   | ns    |

| SCK rising to SDI hold time <sup>3</sup>                            | t <sub>DH</sub>   | 15  | _   | ns    |

| Rise time of SCK and SDI <sup>4</sup>                               | t <sub>R2</sub>   | _   | 100 | ns    |

| Fall time of SCK and SDI <sup>4</sup>                               | t <sub>F2</sub>   | _   | 100 | ns    |

| Delay from supply voltage stable to control port ready <sup>5</sup> | t <sub>DPOR</sub> | _   | 200 | μs    |

1.SPI control-port timing.{172}

- $2.t_{SPI}$  is only needed before first falling edge of  $\overline{CS}$  after power is applied;  $t_{SPI}$  is 0 all other times.

- 3. Data must be held for sufficient time to bridge the transition time of SCK.

- $4.For f_{SCK} < 1 MHz.$

- 5. The supply voltage is considered stable after VDD is within the specified operating conditions (see Table 3-4).

### 4 Revision History

#### Table 4-1. Revision History

| Revision | Change           |

|----------|------------------|

| R2       | Initial revision |

| JUL 2023 |                  |

#### Important:

Please check to confirm that you are using the latest revision of this document and to determine whether there are errata associated with this device.

### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find one nearest you, go to www.cirrus.com.

#### IMPORTANT NOTICE

"Target" product information describes products that are in development and subject to substantial development changes. For the purposes of our terms and conditions of sale, "Preliminary" or "Advanced" data sheets are nonfinal data sheets that include, but are not limited to, data sheets marked as "Target," "Advance," "Product Preview," "Preliminary Technical Data," and/or "Preproduction." Products provided with any such data sheet are therefore subject to relevant terms and conditions associated with "Preliminary" or "Advanced" designations. The products and services of Cirrus Logic International (UK) Limited; Cirrus Logic, Inc.; and other companies in the Cirrus Logic group (collectively either "Cirrus Logic" or "Cirrus") are sold subject to Cirrus Logic's terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. Software is provided pursuant to applicable license terms. Cirrus Logic reserves the right to make changes to its products and specifications or to discontinue any product or service. Customers should therefore obtain the latest version of relevant information from Cirrus Logic to verify that the information is current and complete. Testing and other quality control techniques are utilized to the extent Cirrus Logic deems necessary. Specific testing of all parameters of each device is not necessarily performed. In order to minimize risks associated with customer applications, the customer must use adequate design and operating safeguards to minimize inherent or procedural hazards. Cirrus Logic is not liable for applications assistance or customer product design. The customer is solely responsible for its product design, including the specific manner in which it uses Cirrus Logic components, and certain uses or product designs may require an intellectual property license from a third party. Customers are responsible for overall system design, and system security. While Cirrus Logic is confident in th

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS LOGIC PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, NUCLEAR SYSTEMS, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS LOGIC PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS LOGIC DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS LOGIC PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS LOGIC PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS LOGIC, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

This document is the property of Cirrus Logic, and you may not use this document in connection with any legal analysis concerning Cirrus Logic products described herein. No license to any technology or intellectual property right of Cirrus Logic or any third party is granted herein, including but not limited to any patent right, copyright, mask work right, or other intellectual property rights. Any provision or publication of any third party's products or services does not constitute Cirrus Logic's approval, license, warranty or endorsement thereof. Cirrus Logic gives consent for copies to be made of the information contained herein only for use within your organization with respect to Cirrus Logic integrated circuits or other products of Cirrus Logic, and only if the reproduction is without alteration and is accompanied by all associated copyright, proprietary and other notices and conditions (including this notice). This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. This document and its information is provided "AS IS" without warranty of any kind (express or implied). All statutory warranties and conditions are excluded to the fullest extent possible. No responsibility is assumed by Cirrus Logic for the use of information herein, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. Cirrus Logic, Cirrus, the Cirrus Logic logo design, and SoundClear are among the trademarks of Cirrus Logic. Other brand and product names may be trademarks or service marks of their respective owners.

$Copyright @ 2023 \ Cirrus \ Logic, Inc. \ and \ Cirrus \ Logic \ International \ Semiconductor \ Ltd. \ All \ rights \ reserved.$