## PC Codec with Headphone, MIC Interface and Class D Speaker Drivers

#### System Features

- Stereo headphone (HP) output with 114 dB dynamic range

- Class H headphone amplifier with automatic or manual supply adjust

- $-2 \times 33.7$  mW power output at -85 dB THD+N into 30  $\Omega$

- 1  $V_{RMS}$  output swing into 30  $\Omega$  loads

- Load detection

- · Mono mic/stereo line input with 94 dB dynamic range

- Headset bias with integrated bias resistor

- 1 V<sub>RMS</sub> input voltage

- Programmable analog front end (AFE) gain from –6 to +18 dB in 6 dB steps

- · Integrated detect features

- OMTP (Open Mobile Terminal Platform) and CTIA headset-type detection and configuration with low-impedance internal switches

- Mic button press detect with ADC automute

- Mic button detection compatible with Android Wired Headset Specification (Version 1.1)

- Automatic Hi-Z of headset bias output on headset bias current drop or HP/headset unplug

- · Stereo Class D Bridge-tied load (BTL) speaker driver

- 2 W @ 1% THD+N into 4 Ω load

- 102 dB dynamic range

- System wake from headset/headphone plug/unplug or mic button press

- Stereo three-band parametric equalizers

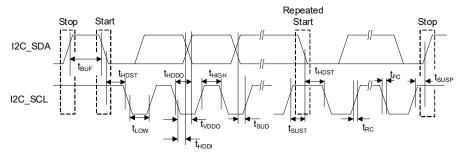

- I2C control supporting rates up to Fast Mode Plus

- MIPI® SoundWire® v1.2.1 interface with SDCA support

- S/PDIF transmit (Sony/Philips digital interface format)

- · Integrated fractional-N PLL

- Allows multiple clock input rates

- Reference clock sourced from either SoundWire clock or external MCLK IN source

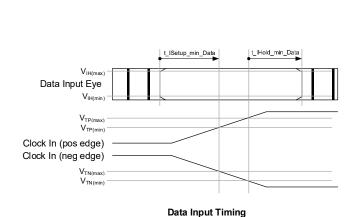

- · PDM input for digital microphones

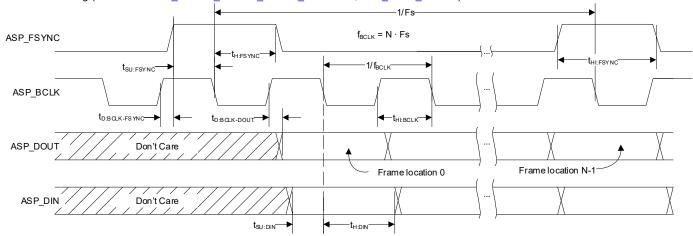

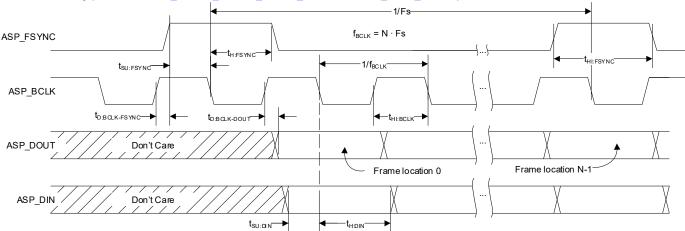

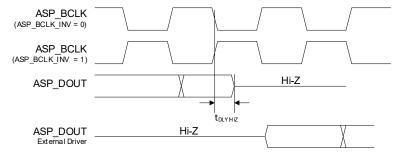

- Audio serial port (ASP)

- I<sup>2</sup>S (two channels) or TDM (up to six channels)

- Master or Slave Mode

- Sample rate support for 8 to 192 kHz

- · Integrated power management

- Digital core can be supplied externally, or by an internal LDO from the VDD\_IO supply

- Step-up/down charge pump improves HP efficiency

- VDD\_P monitor to detect and report brownout conditions

## **Applications**

Laptops, desktops, ultrabooks, and Chromebooks

#### **General Description**

The CS42L43 is an audio codec with integrated MIPI SoundWire interface (Version 1.2.1 compliant), I<sup>2</sup>C, SPI, and I<sup>2</sup>S/TDM interfaces designed for portable applications. It provides a high dynamic range, stereo DAC for headphone output, two integrated Class D amplifiers for loudspeakers, and two ADCs for wired headset microphone input or stereo line input. PDM inputs are provided for digital microphones.

The CS42L43 provides high performance audio capture from the ADC and PDM inputs and audio playback to the headphone DACs, Class D speaker drivers, and an IEC-60958-3-compatible S/PDIF transmitter. The CS42L43 includes assignable SRCs and an assignable stereo, three-band, 32-bit, parametric equalizer.

Digital mixers are available with independent attenuation on each mixer input.

Digital volume/mute control is available on all capture and playback paths and selectable high-pass filters are available on the capture paths for removal of DC offsets or wind noise suppression.

A headset mic bias with an integrated pull-up resistor is provided for use with the headset interface. Other headset features include automatic headset type detection (OMTP/CTIA-compliant), mic-bias/ground switching, and headset-button detection including Android Wired Headset Specification v1.1. Other features include insert/removal detection, headphone load impedance detection, and stereo line-in support.

The CS42L43 can be configured to provide a bridge between a SoundWire host and the SPI master and ASP ports. This enables non-SoundWire audio peripherals such as additional speaker amplifiers or a companion DSP to be integrated alongside a SoundWire host system.

A high performance fractional PLL is available for generating internal audio sample clocks.

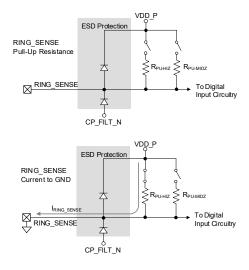

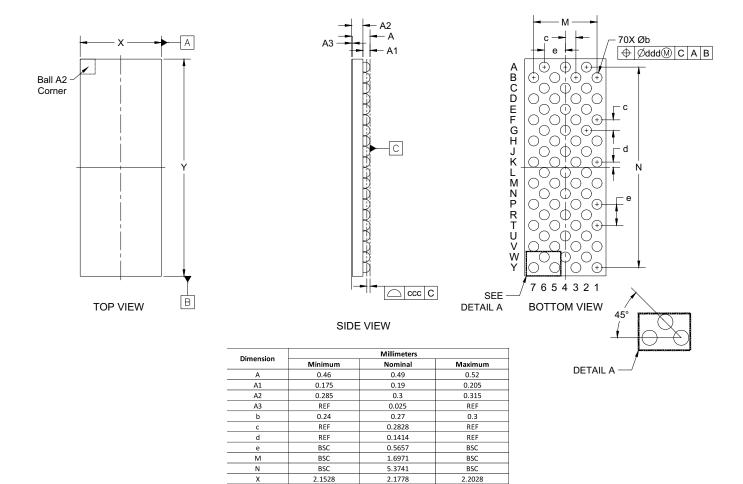

The CS42L43 is available in a commercial-grade, 70-ball WLCSP (wafer-level chip scale package) and a commercial-grade, 88-pin QFN package for operation between –40°C to +85°C. Note that the WLCSP package can be routed using standard PCB with vias in many applications.

See Section 7 for ordering information.

## 1 Pin Assignments and Descriptions

This section shows pin assignments and describes pin functions.

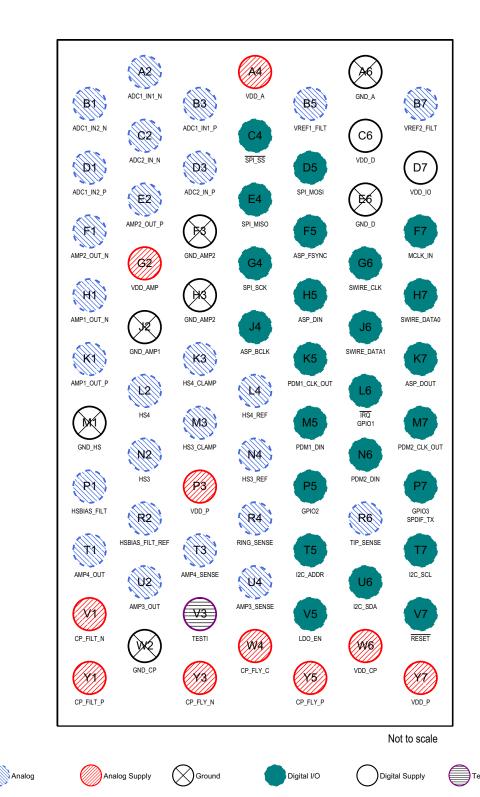

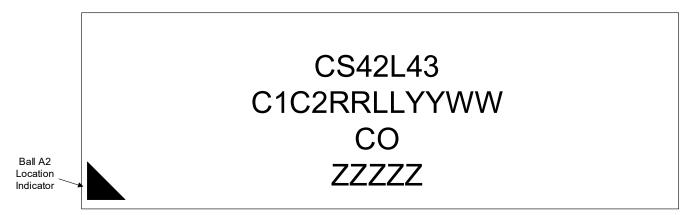

## 1.1 WLCSP Pin Out (Through-Package, Top View)

Figure 1-1. WLCSP Pin Diagram (Through-Package, Top View)

## 1.2 WLCSP Pin Descriptions

Table 1-1. WLCSP Pin Descriptions

| Pin Name   | Ball # | Power<br>Supply | I/O | Description                                                                                                                                                                                                    | Internal<br>Connection | State at<br>Reset |

|------------|--------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| ADC1_IN1_N | A2     | VDD_P           | I   | Inverting analog input for ADC 1 mux input 1.                                                                                                                                                                  | _                      | _                 |

| ADC1_IN1_P | В3     | VDD_P           | I   | Non-inverting analog input for ADC 1 mux input 1.                                                                                                                                                              | _                      | _                 |

| ADC1_IN2_N | B1     | VDD_P           | I   | Inverting analog input for ADC 1 mux input 2.                                                                                                                                                                  | _                      | _                 |

| ADC1_IN2_P | D1     | VDD_P           | I   | Non-inverting analog input for ADC 1 mux input 2.                                                                                                                                                              | _                      | _                 |

| ADC2_IN_N  | C2     | VDD_P           | I   | Inverting analog input for ADC2.                                                                                                                                                                               | _                      | _                 |

| ADC2_IN_P  | D3     | VDD_P           | I   | Non-inverting analog input for ADC 2.                                                                                                                                                                          | _                      | _                 |

| AMP1_OUT_N | H1     | VDD_AMP         | 0   | <b>Amplifier 1 Negative Output.</b> This amplifier is typically used to drive the negative-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP1_OUT_P | K1     | VDD_AMP         | 0   | <b>Amplifier 1 Positive Output.</b> This amplifier is typically used to drive the positive-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP2_OUT_N | F1     | VDD_AMP         | 0   | <b>Amplifier 2 Negative Output.</b> This amplifier is typically used to drive the negative-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP2_OUT_P | E2     | VDD_AMP         | 0   | <b>Amplifier 2 Positive Output.</b> This amplifier is typically used to drive the positive-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP3_OUT   | U2     | CP_FILT_P/N     | 0   | <b>Amplifier 3 Output.</b> Ground-centered audio output typically used for headphone speakers and connects to TIP (HS1).                                                                                       | -                      | _                 |

| AMP3_SENSE | U4     | CP_FILT_P/N     | I   | Amplifier 3 Feedback Sense Input.                                                                                                                                                                              | _                      | _                 |

| AMP4_OUT   | T1     | CP_FILT_P/N     | 0   | <b>Amplifier 4 Output.</b> Ground-centered audio output typically used for headphone speakers and connects to RING1 (HS2).                                                                                     | <del>_</del>           | _                 |

| AMP4_SENSE | Т3     | CP_FILT_P/N     | I   | Amplifier 4 Feedback Sense Input.                                                                                                                                                                              | _                      | _                 |

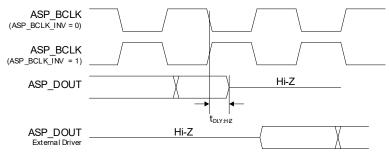

| ASP_BCLK   | J4     | VDD_IO          | I/O | ASP Bit Clock. Serial shift clock for the interface.                                                                                                                                                           | Weak pull<br>down      | Weak pull<br>down |

| ASP_DIN    | H5     | VDD_IO          | I   | <b>ASP Data Input.</b> Input for two's complement serial PCM audio data.                                                                                                                                       | Weak pull<br>down      | Weak pull<br>down |

| ASP_DOUT   | K7     | VDD_IO          | 0   | <b>ASP Data Output.</b> Output for two's complement serial PCM audio data.                                                                                                                                     | Weak pull<br>down      | Weak pull<br>down |

| ASP_FSYNC  | F5     | VDD_IO          | I/O | ASP Frame Sync Clock. Identifies the start of each serialized PCM data word and indicates which channel, left or right, is active on the serial PCM audio data lines or indicates the start of each TDM frame. | Weak pull<br>down      | Weak pull<br>down |

| CP_FILT_N  | V1     | Power           | 0   | <b>Inverting Charge Pump Filter Connection.</b> Power supply for the inverting charge pump that provides the negative rail for amplifiers 3 and 4.                                                             | _                      | _                 |

| CP_FILT_P  | Y1     | Power           | 0   | Step-Up/Down Charge Pump Filter Connection. Power supply for the step-up/down charge pump that provides the positive rail for amplifiers 3 and 4.                                                              | _                      | _                 |

| CP_FLY_C   | W4     | VDD_P           | 0   | <b>Charge Pump Cap Common Node.</b> Common positive node for amplifiers 3 and 4 step-down and inverting charge pumps' flying capacitors.                                                                       | _                      | _                 |

| CP_FLY_N   | Y3     | CP_FILT_P       | 0   | Charge Pump Cap Negative Node. Negative node for amplifiers 3 and 4 step-up/down charge-pump flying capacitor.                                                                                                 | _                      | _                 |

| CP_FLY_P   | Y5     | VDD_P           | 0   | <b>Charge Pump Cap Positive Node.</b> Positive node for amplifiers 3 and 4 step-up/down charge-pump flying capacitor.                                                                                          | _                      | _                 |

| GND_A      | A6     | Power           | I   | Analog Ground. Ground reference for the internal analog circuits.                                                                                                                                              |                        | _                 |

| GND_AMP1   | J2     | Power           | I   | <b>Amplifier 1 Output Ground.</b> This amplifier is typically used to drive a low impedance speaker.                                                                                                           | _                      | _                 |

| GND_AMP2   | F3, H3 | Power           | I   | <b>Amplifier 2 Output Ground.</b> This amplifier is typically used to drive a low impedance speaker.                                                                                                           | _                      | _                 |

#### Table 1-1. WLCSP Pin Descriptions (Cont.)

| Pin Name            | Pin Name Ball # Power Supply I/O Description |        | Internal<br>Connection | State at Reset                                                                                                                                                                                 |                   |                   |

|---------------------|----------------------------------------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| GND_CP              | W2                                           | Power  | I                      | <b>Charge Pump Ground.</b> Ground reference for amplifiers 3 and 4 charge pump.                                                                                                                | _                 | _                 |

| GND_D               | E6                                           | Power  | I                      | <b>Digital Ground.</b> Ground reference for the internal digital circuits.                                                                                                                     | _                 | _                 |

| GND_HS              | M1                                           | Power  | I                      | <b>Headset Ground.</b> Ground reference for the internal headset analog circuits.                                                                                                              | _                 | _                 |

| GPIO2               | P5                                           | VDD_IO | I/O                    | General Purpose Input/Output 2.                                                                                                                                                                | Weak pull<br>up   | Weak pull<br>up   |

| GPIO3/<br>SPDIF_TX  | P7                                           | VDD_IO | I/O                    | General Purpose Input/Output 3.  S/PDIF Audio Serial Data Output. Serial data output for S/ PDIF interface.                                                                                    | Weak pull<br>down | Weak pull<br>down |

| HS3                 | N2                                           | VDD_P  | I                      | <b>Headset Connection.</b> Input to headset and mic-button detection functions.                                                                                                                | _                 | _                 |

| HS3_CLAMP           | М3                                           | VDD_P  | I                      | Headset Depletion FET Connections. Input to drain of integrated depletion FET for ground-noise rejection.                                                                                      | _                 | _                 |

| HS3_REF             | N4                                           | VDD_P  | I                      | <b>Headset Connection Reference.</b> Input to pseudodifferential amplifier 3 and 4 output reference.                                                                                           | _                 | _                 |

| HS4                 | L2                                           | VDD_P  | I                      | <b>Headset Connection.</b> Input to headset and mic-button detection functions.                                                                                                                | _                 | _                 |

| HS4_CLAMP           | K3                                           | VDD_P  | I                      | Headset Depletion FET Connections. Input to drain of integrated depletion FET for ground-noise rejection.                                                                                      | _                 | _                 |

| HS4_REF             | L4                                           | VDD_P  | I                      | <b>Headset Connection Reference.</b> Input to pseudodifferential amplifier 3 and 4 output reference.                                                                                           | _                 | _                 |

| HSBIAS_FILT         | P1                                           | VDD_P  | I                      | <b>Headset Bias Source Voltage Filter.</b> Filter connection for the internal bias voltage used for headset bias.                                                                              | _                 | _                 |

| HSBIAS_FILT_<br>REF | R2                                           | VDD_P  | I                      | Headset Bias Source Voltage Filter Reference. Input of filter connection for the internal headset bias voltage.                                                                                | _                 | _                 |

| I2C_ADDR            | T5                                           | VDD_IO | I                      | <b>I<sup>2</sup>C Address Input</b> . Address pin for the I <sup>2</sup> C target address and the SoundWire Unique ID. Latched on POR, hard, or soft reset. Connect this pin to VDD_IO or GND. | Weak pull<br>down | Weak pull<br>down |

| I2C_SCL             | T7                                           | VDD_IO | I                      | I2C Clock. Clock input for the I2C interface.                                                                                                                                                  | _                 | _                 |

| I2C_SDA             | U6                                           | VDD_IO | I/O                    | I2C Input/Output. Data input/output for the I2C interface.                                                                                                                                     | _                 | _                 |

| ĪRQ/GPIO1           | L6                                           | VDD_IO | I/O                    | Interrupt output. Programmable, open-drain, active-low programmable interrupt output.  General Purpose Input/Output 1.                                                                         | Weak pull<br>up   | Weak pull<br>up   |

| LDO_EN              | V5                                           | VDD_P  | I                      | LDO Enable. Digital core logic LDO enable.                                                                                                                                                     | Weak pull<br>down | Weak pull<br>down |

| MCLK_IN             | F7                                           | VDD_IO | I                      | <b>Main Clock Input.</b> Clock source for the device core, serial port mastering, and converters.                                                                                              | Weak pull<br>down | Weak pull<br>down |

| PDM1_CLK_OUT        | K5                                           | VDD_IO | 0                      | PDM 1 Bit Clock Output.                                                                                                                                                                        | Weak pull<br>down | Weak pull<br>down |

| PDM1_DIN            | M5                                           | VDD_IO | I                      | PDM 1 Data Input.                                                                                                                                                                              | Weak pull<br>down | Weak pull<br>down |

| PDM2_CLK_OUT        | M7                                           | VDD_IO | 0                      | PDM 2 Bit Clock Output.                                                                                                                                                                        | Weak pull<br>down | Weak pull<br>down |

| PDM2_DIN            | N6                                           | VDD_IO | I                      | PDM 2 Data Input.                                                                                                                                                                              | Weak pull<br>down | Weak pull<br>down |

| RESET               | V7                                           | VDD_P  | I                      | <b>Reset.</b> The device enters a low power mode when this pin is driven low.                                                                                                                  | Weak pull<br>down | Weak pull<br>down |

| RING_SENSE          | R4                                           | VDD_P  | I                      | Ring Sense Input. Sense pin to detect headphone plug. Can be configured to be debounced on plug and unplug events independently.                                                               | _                 | _                 |

| SPI_MISO            | E4                                           | VDD_IO | I                      | <b>SPI Slave Out Master In.</b> SPI serial data where the slave device is the transmitter and the master device is the receiver.                                                               | Weak pull<br>down | Weak pull<br>down |

#### Table 1-1. WLCSP Pin Descriptions (Cont.)

| Pin Name    | Name Ball # Power I/O Description |        | Internal<br>Connection | State at<br>Reset                                                                                                                                          |                   |                   |

|-------------|-----------------------------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| SPI_MOSI    | D5                                | VDD_IO | 0                      | <b>SPI Master Out Slave In.</b> SPI serial data where the master device is the transmitter and the slave device is the receiver.                           | Weak pull<br>down | Weak pull<br>down |

| SPI_SCK     | G4                                | VDD_IO | 0                      | SPI Serial Data Clock. The bit clock for the data on the SPI_MOSI and SPI_MISO pins.                                                                       | Weak pull<br>down | Weak pull<br>down |

| SPI_SS      | C4                                | VDD_IO | 0                      | SPI Slave Select. SPI slave device select.                                                                                                                 | Weak pull<br>up   | Weak pull<br>up   |

| SWIRE_CLK   | G6                                | VDD_IO | I                      | <b>SoundWire Serial Clock Input.</b> Clock input to the SoundWire peripheral interface.                                                                    | _                 | _                 |

| SWIRE_DATA0 | H7                                | VDD_IO | I/O                    | SoundWire Serial Data Input and Output 0. Primary serial data input and output of the SoundWire peripheral interface.                                      | _                 | _                 |

| SWIRE_DATA1 | J6                                | VDD_IO | I/O                    | <b>SoundWire Serial Data Input and Output 1.</b> Serial data input and output of the SoundWire peripheral interface.                                       | _                 | _                 |

| TESTI       | V3                                | _      | I                      | Test Input Pin. Must be connected to ground.                                                                                                               | _                 | _                 |

| TIP_SENSE   | R6                                | VDD_P  | I                      | <b>Tip Sense.</b> Sense pin to detect headphone plug. Can be set to wake the system. Independently configurable to be debounced on plug and unplug events. | _                 | _                 |

| VDD_A       | A4                                | Power  | I                      | Analog Power Supply. Power supply for internal analog circuits.                                                                                            | _                 | _                 |

| VDD_AMP     | G2                                | Power  | I                      | Amplifiers 1 and 2 Power Supply.                                                                                                                           | _                 | _                 |

| VDD_CP      | W6                                | Power  | I                      | <b>Charge Pump Power.</b> Power supply for amplifiers 3 and 4 charge pump.                                                                                 | _                 | _                 |

| VDD_D       | C6                                | Power  | I                      | <b>Digital Core Power Supply.</b> Power supply for internal digital circuits.                                                                              | _                 | _                 |

| VDD_IO      | D7                                | Power  | I                      | I/O Power Supply. Power supply for external interface and internal digital logic.                                                                          | _                 | _                 |

| VDD_P       | P3, Y7                            | Power  | I                      | <b>High Voltage Supply.</b> Power supply for the high voltage interface.                                                                                   | _                 | _                 |

| VREF1_FILT  | B5                                | VDD_A  | I                      | <b>Voltage Reference.</b> Reference voltage for internal ADCs and amplifiers 3 and 4.                                                                      | _                 | _                 |

| VREF2_FILT  | В7                                | VDD_A  | I                      | <b>Voltage Reference.</b> Reference voltage for internal amplifiers 1 and 2.                                                                               | _                 |                   |

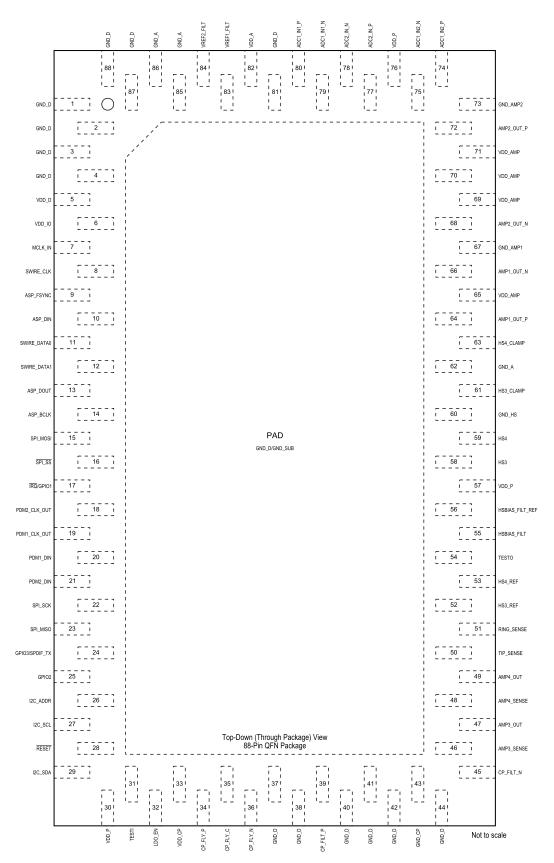

## 1.3 QFN Pin Out (Through-Package, Top View)

Figure 1-2. QFN Pin Diagram (Through-Package, Top View)

## 1.4 QFN Pin Descriptions

Table 1-2. QFN Pin Descriptions

| Pin Name   | Ball #        | Power<br>Supply | I/O | Description                                                                                                                                                                                                    | Internal<br>Connection | State at<br>Reset |

|------------|---------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| ADC1_IN1_N | 79            | VDD_P           | I   | Inverting analog input for ADC 1 mux input 1.                                                                                                                                                                  | _                      | _                 |

| ADC1_IN1_P | 80            | VDD_P           | I   | Non-inverting analog input for ADC 1 mux input 1.                                                                                                                                                              | _                      | _                 |

| ADC1_IN2_N | 75            | VDD_P           | I   | Inverting analog input for ADC 1 mux input 2.                                                                                                                                                                  | _                      | _                 |

| ADC1_IN2_P | 74            | VDD_P           | ı   | Non-inverting analog input for ADC 1 mux input 2.                                                                                                                                                              | _                      | _                 |

| ADC2_IN_N  | 78            | VDD_P           | ı   | Inverting analog input for ADC 2.                                                                                                                                                                              | _                      | _                 |

| ADC2_IN_P  | 77            | VDD_P           | ı   | Non-inverting analog input for ADC 2.                                                                                                                                                                          | _                      | _                 |

| AMP1_OUT_N | 66            | VDD_AMP         | 0   | <b>Amplifier 1 Negative Output.</b> This amplifier is typically used to drive the negative-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP1_OUT_P | 64            | VDD_AMP         | 0   | <b>Amplifier 1 Positive Output.</b> This amplifier is typically used to drive the positive-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP2_OUT_N | 68            | VDD_AMP         | 0   | <b>Amplifier 2 Negative Output.</b> This amplifier is typically used to drive the negative-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP2_OUT_P | 72            | VDD_AMP         | 0   | <b>Amplifier 2 Positive Output.</b> This amplifier is typically used to drive the positive-side of a differentially connected low impedance speaker.                                                           | _                      | _                 |

| AMP3_OUT   | 47            | CP_FILT_P/N     | 0   | Amplifier 3 Output. Ground-centered audio output typically used for headphone speakers and connects to TIP (HS1).                                                                                              | _                      | _                 |

| AMP3_SENSE | 46            | CP_FILT_P/N     | I   | Amplifier 3 Feedback Sense Input.                                                                                                                                                                              | _                      | _                 |

| AMP4_OUT   | 49            | CP_FILT_P/N     | 0   | <b>Amplifier 4 Output.</b> Ground-centered audio output typically used for headphone speakers and connects to RING1 (HS2).                                                                                     | _                      | _                 |

| AMP4_SENSE | 48            | CP_FILT_P/N     | ı   | Amplifier 4 Feedback Sense Input.                                                                                                                                                                              | _                      | _                 |

| ASP_BCLK   | 14            | VDD_IO          | I/O | ASP Bit Clock. Serial shift clock for the interface.                                                                                                                                                           | Weak pull<br>down      | Weak pull<br>down |

| ASP_DIN    | 10            | VDD_IO          | I   | ASP Data Input. Input for two's complement serial PCM audio data.                                                                                                                                              | Weak pull<br>down      | Weak pull<br>down |

| ASP_DOUT   | 13            | VDD_IO          | 0   | ASP Data Output. Output for two's complement serial PCM audio data.                                                                                                                                            | Weak pull<br>down      | Weak pull<br>down |

| ASP_FSYNC  | 9             | VDD_IO          | I/O | ASP Frame Sync Clock. Identifies the start of each serialized PCM data word and indicates which channel, left or right, is active on the serial PCM audio data lines or indicates the start of each TDM frame. | Weak pull<br>down      | Weak pull<br>down |

| CP_FILT_N  | 45            | Power           | 0   | <b>Inverting Charge Pump Filter Connection.</b> Power supply for the inverting charge pump that provides the negative rail for amplifiers 3 and 4.                                                             | _                      | _                 |

| CP_FILT_P  | 39            | Power           | 0   | <b>Step-Up/Down Charge Pump Filter Connection.</b> Power supply for the step-up/down charge pump that provides the positive rail for amplifiers 3 and 4.                                                       | _                      | _                 |

| CP_FLY_C   | 35            | VDD_P           | 0   | <b>Charge Pump Cap Common Node.</b> Common positive node for amplifiers 3 and 4 step-down and inverting charge pumps' flying capacitors.                                                                       | _                      | _                 |

| CP_FLY_N   | 36            | CP_FILT_P       | 0   | <b>Charge Pump Cap Negative Node.</b> Negative node for amplifiers 3 and 4 step-up/down charge-pump flying capacitor.                                                                                          | <del></del>            | _                 |

| CP_FLY_P   | 34            | VDD_P           | 0   | <b>Charge Pump Cap Positive Node.</b> Positive node for amplifiers 3 and 4 step-up/down charge-pump flying capacitor.                                                                                          |                        |                   |

| GND_A      | 62, 85,<br>86 | Power           | I   | <b>Analog Ground.</b> Ground reference for the internal analog circuits.                                                                                                                                       | _                      | _                 |

| GND_AMP1   | 67            | Power           | I   | <b>Amplifier 1 Output Ground.</b> This amplifier is typically used to drive a low impedance speaker.                                                                                                           | _                      | _                 |

#### Table 1-2. QFN Pin Descriptions (Cont.)

|                     | Pin Name Ball # Power I/O Description                            |        | Connection | State at<br>Reset                                                                                                                                                     |                   |                   |

|---------------------|------------------------------------------------------------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| GND_AMP2            | 73                                                               | Power  | I          | <b>Amplifier 2 Output Ground.</b> This amplifier is typically used to drive a low impedance speaker.                                                                  | _                 | _                 |

| GND_CP              | 43                                                               | Power  | I          | <b>Charge Pump Ground.</b> Ground reference for amplifiers 3 and 4 charge pump.                                                                                       | _                 | _                 |

| GND_D               | 1, 2,<br>3, 4,<br>37, 38,<br>40, 41,<br>42, 44,<br>81, 87,<br>88 | Power  | I          | Digital Ground. Ground reference for the internal digital circuits.                                                                                                   | _                 | _                 |

| GND_D/<br>GND_SUB   | PAD                                                              | Power  | I          | <b>Digital Ground.</b> Ground reference for the internal digital circuits. <b>Substrate Ground</b> .                                                                  | _                 | _                 |

| GND_HS              | 60                                                               | Power  | I          | <b>Headset Ground.</b> Ground reference for the internal headset analog circuits.                                                                                     | _                 | _                 |

| GPIO2               | 25                                                               | VDD_IO | I/O        | General Purpose Input/Output 2.                                                                                                                                       | Weak pull<br>up   | Weak pull<br>up   |

| GPIO3/<br>SPDIF_TX  | 24                                                               | VDD_IO | I/O        | General Purpose Input/Output 3. S/PDIF Audio Serial Data Output. Serial data output for S/PDIF interface.                                                             | Weak pull<br>down | Weak pull<br>down |

| HS3                 | 58                                                               | VDD_P  | I          | <b>Headset Connection.</b> Input to headset and mic-button detection functions.                                                                                       | _                 | _                 |

| HS3_CLAMP           | 61                                                               | VDD_P  | I          | Headset Depletion FET Connections. Input to drain of integrated depletion FET for ground-noise rejection.                                                             | _                 | _                 |

| HS3_REF             | 52                                                               | VDD_P  | I          | <b>Headset Connection Reference.</b> Input to pseudodifferential amplifier 3 and 4 output reference.                                                                  | _                 | _                 |

| HS4                 | 59                                                               | VDD_P  | I          | <b>Headset Connection.</b> Input to headset and mic-button detection functions.                                                                                       | _                 | _                 |

| HS4_CLAMP           | 63                                                               | VDD_P  | I          | Headset Depletion FET Connections. Input to drain of integrated depletion FET for ground-noise rejection.                                                             | <del></del>       | _                 |

| HS4_REF             | 53                                                               | VDD_P  | I          | <b>Headset Connection Reference</b> . Input to pseudodifferential amplifier 3 and 4 output reference.                                                                 |                   | _                 |

| HSBIAS_FILT         | 55                                                               | VDD_P  | I          | <b>Headset Bias Source Voltage Filter.</b> Filter connection for the internal bias voltage used for headset bias.                                                     | _                 | _                 |

| HSBIAS_FILT_<br>REF | 56                                                               | VDD_P  | I          | <b>Headset Bias Source Voltage Filter Reference.</b> Input of filter connection for the internal headset bias voltage.                                                | _                 | _                 |

| I2C_ADDR            | 26                                                               | VDD_IO | I          | <b>I2C Address Input.</b> Address pin for the I2C target address and the SoundWire Unique ID. Latched on POR, hard, or soft reset. Connect this pin to VDD_IO or GND. | Weak pull<br>down | Weak pull<br>down |

| I2C_SCL             | 27                                                               | VDD_IO | I          | I2C Clock. Clock input for the I2C interface.                                                                                                                         | _                 |                   |

| I2C_SDA             | 29                                                               | VDD_IO | I/O        | I2C Input/Output. Data input/output for the I2C interface.                                                                                                            | _                 | _                 |

| ĪRQ/GPIO1           | 17                                                               | VDD_IO | I/O        | Interrupt output. Programmable, open-drain, active-low programmable interrupt output.  General Purpose Input/Output 1.                                                | Weak pull<br>up   | Weak pull<br>up   |

| LDO_EN              | 32                                                               | VDD_P  | I          | LDO Enable. Digital core logic LDO enable.                                                                                                                            | Weak pull<br>down | Weak pull<br>down |

| MCLK_IN             | 7                                                                | VDD_IO | I          | <b>Main Clock Input.</b> Clock source for the device core, serial port mastering, and converters.                                                                     | Weak pull<br>down | Weak pull<br>down |

| PDM1_CLK_OUT        | 19                                                               | VDD_IO | 0          | PDM 1 Bit Clock Output.                                                                                                                                               | Weak pull<br>down | Weak pull<br>down |

| PDM1_DIN            | 20                                                               | VDD_IO | I          | PDM 1 Data Input.                                                                                                                                                     | Weak pull<br>down | Weak pull<br>down |

| PDM2_CLK_OUT        | 18                                                               | VDD_IO | 0          | PDM 2 Bit Clock Output.                                                                                                                                               | Weak pull<br>down | Weak pull<br>down |

| PDM2_DIN            | 21                                                               | VDD_IO | I          | PDM 2 Data Input.                                                                                                                                                     | Weak pull<br>down | Weak pull<br>down |

#### Table 1-2. QFN Pin Descriptions (Cont.)

| Pin Name    | Ball #            | Power<br>Supply | I/O | Description                                                                                                                                                | Internal<br>Connection | State at<br>Reset |

|-------------|-------------------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| RESET       | 28                | VDD_P           | I   | <b>Reset.</b> The device enters a low power mode when this pin is driven low.                                                                              | Weak pull<br>down      | Weak pull<br>down |

| RING_SENSE  | 51                | VDD_P           | I   | Ring Sense Input. Sense pin to detect headphone plug. Can be configured to be debounced on plug and unplug events independently.                           | _                      | _                 |

| SPI_MISO    | 23                | VDD_IO          | I   | <b>SPI Slave Out Master In.</b> SPI serial data where the slave device is the transmitter and the master device is the receiver.                           | Weak pull<br>down      | Weak pull<br>down |

| SPI_MOSI    | 15                | VDD_IO          | 0   | <b>SPI Master Out Slave In.</b> SPI serial data where the master device is the transmitter and the slave device is the receiver.                           | Weak pull<br>down      | Weak pull<br>down |

| SPI_SCK     | 22                | VDD_IO          | 0   | SPI Serial Data Clock. The bit clock for the data on the SPI_MOSI and SPI_MISO pins.                                                                       | Weak pull<br>down      | Weak pull<br>down |

| SPI_SS      | 16                | VDD_IO          | 0   | SPI Slave Select. SPI slave device select.                                                                                                                 | Weak pull<br>up        | Weak pull<br>up   |

| SWIRE_CLK   | 8                 | VDD_IO          | I   | <b>SoundWire Serial Clock Input.</b> Clock input to the SoundWire peripheral interface.                                                                    | _                      | _                 |

| SWIRE_DATA0 | 11                | VDD_IO          | I/O | <b>SoundWire Serial Data Input and Output 0.</b> Primary serial data input and output of the SoundWire peripheral interface.                               | _                      | _                 |

| SWIRE_DATA1 | 12                | VDD_IO          | I/O | <b>SoundWire Serial Data Input and Output 1.</b> Serial data input and output of the SoundWire peripheral interface.                                       | _                      | _                 |

| TESTI       | 31                | _               | I   | Test Input Pin. Must be connected to ground.                                                                                                               | _                      | _                 |

| TESTO       | 54                | _               | 0   | Test Output Pin. Must be left floating.                                                                                                                    | _                      | _                 |

| TIP_SENSE   | 50                | VDD_P           | I   | <b>Tip Sense.</b> Sense pin to detect headphone plug. Can be set to wake the system. Independently configurable to be debounced on plug and unplug events. | _                      | _                 |

| VDD_A       | 82                | Power           | I   | Analog Power Supply. Power supply for internal analog circuits.                                                                                            | _                      | _                 |

| VDD_AMP     | 65, 69,<br>70, 71 | Power           | I   | Amplifiers 1 and 2 Power Supply.                                                                                                                           | _                      | _                 |

| VDD_CP      | 33                | Power           | I   | <b>Charge Pump Power.</b> Charge pump power supply for amplifiers 3 and 4.                                                                                 | _                      | _                 |

| VDD_D       | 5                 | Power           | I   | <b>Digital Core Power Supply.</b> Power supply for internal digital circuits.                                                                              | _                      | _                 |

| VDD_IO      | 6                 | Power           | I   | I/O Power Supply. Power supply for external interface and internal digital logic.                                                                          |                        | _                 |

| VDD_P       | 30, 57,<br>76     | Power           | I   | <b>High Voltage Supply.</b> Power supply for the high voltage interface.                                                                                   |                        | _                 |

| VREF1_FILT  | 83                | VDD_A           | I   | <b>Voltage Reference.</b> Reference voltage for internal ADCs and amplifiers 3 and 4.                                                                      |                        | _                 |

| VREF2_FILT  | 84                | VDD_A           | I   | <b>Voltage Reference.</b> Reference voltage for internal amplifiers 1 and 2.                                                                               | _                      | _                 |

#### 1.5 Termination of Unused Pins

Some systems may not need to connect to all of the device pins. Table 1-3 shows the recommended termination for any permanently unused pins. A pin that is connected to other circuits but is only occasionally active is not required to follow the terminations shown.

Table 1-3. Recommended Termination of Unused Pins

| Termination            |

|------------------------|

| Float                  |

| rioat                  |

| _                      |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

| 1                      |

| 1                      |

|                        |

|                        |

|                        |

| 1                      |

|                        |

|                        |

| -                      |

| Grounded               |

|                        |

|                        |

| -                      |

|                        |

| 1                      |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

| -                      |

|                        |

|                        |

| -                      |

| -                      |

|                        |

| -                      |

| -                      |

| -                      |

|                        |

| -                      |

| -                      |

| Dullod bird            |

| Pulled high            |

| Float or Tie to VDD_IO |

|                        |

<sup>1.</sup>TESTO is only available in the QFN package.

<sup>2.</sup>AMP3 SENSE must not be grounded if AMP3 OUT is used.

<sup>3.</sup>AMP4\_SENSE must not be grounded if AMP4\_OUT is used.

<sup>4.</sup> While the no connect (NC) pins on the QFN package have no internal connection to circuitry, it is recommended to connect them to GND\_D.

<sup>5.</sup> VDD AMP must be grounded for configurations that do not require speakers.

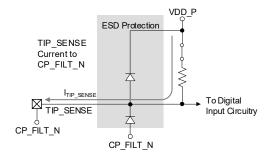

## 1.6 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS42L43 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to JEDEC ESD protection standards JS-001-2017 and JS-001-2018.

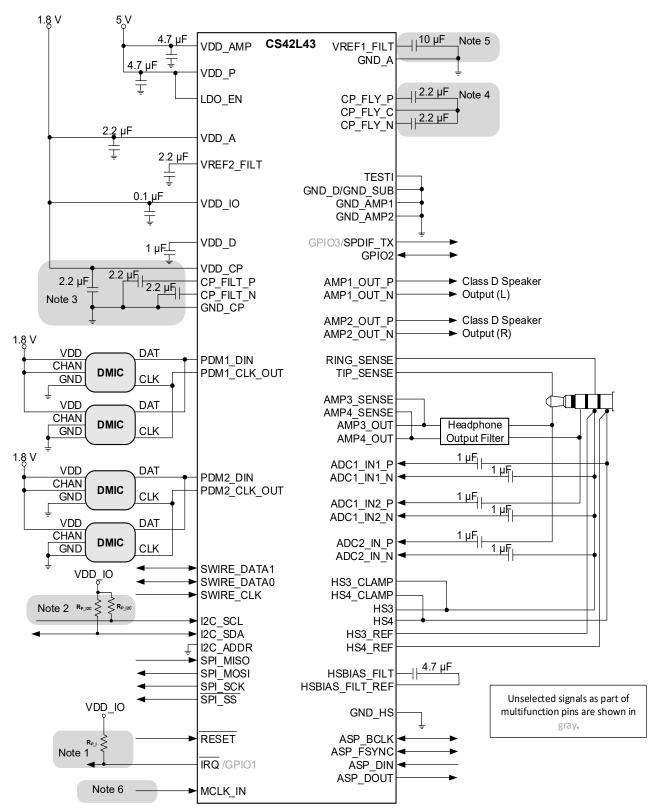

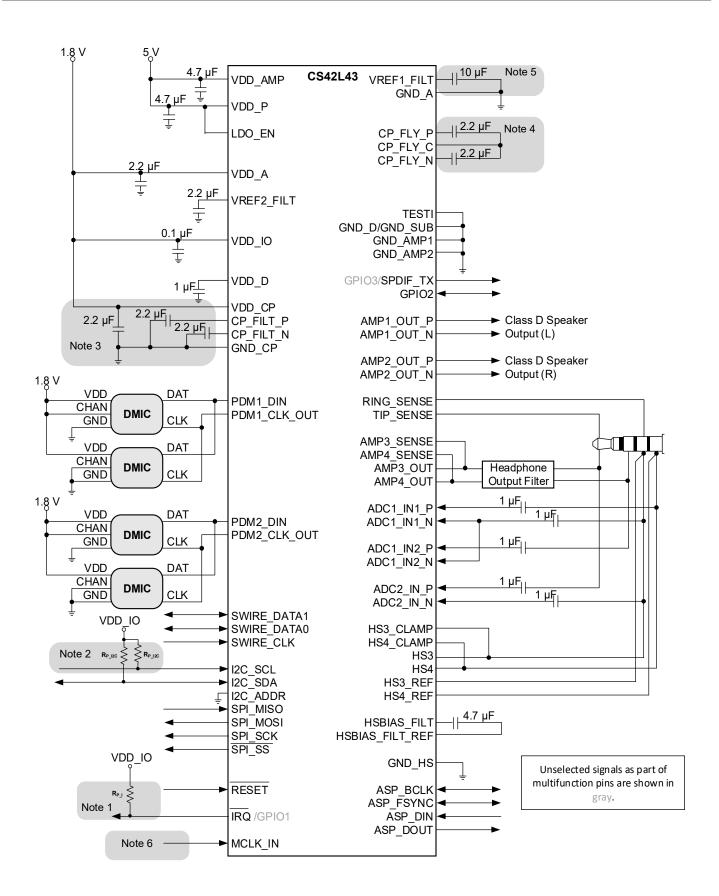

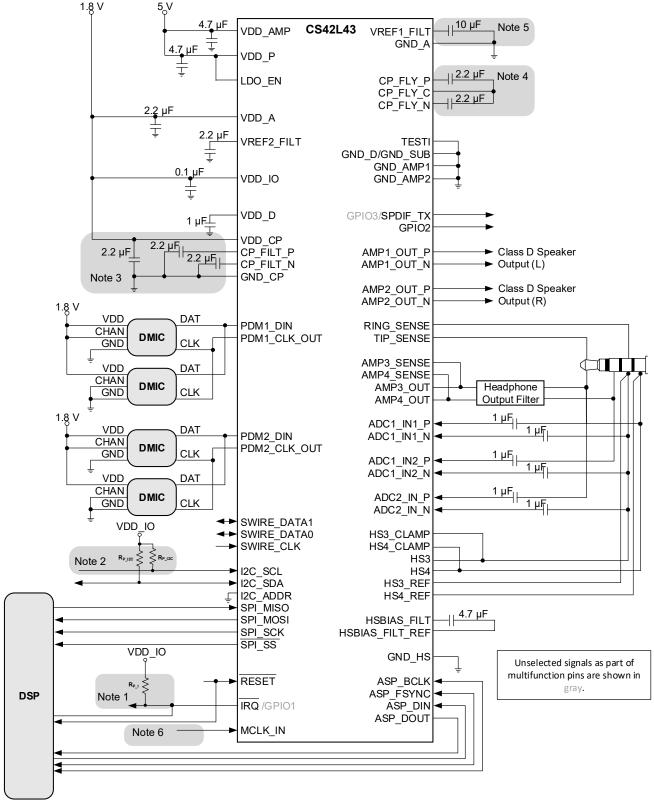

## 2 Typical Connections

## 2.1 Typical Connection Diagrams

Figure 2-1. Typical Connection Diagram—Non-DSP Use Case, Separate ADC1 Ground

Figure 2-2. Typical Connection Diagram—Non-DSP Use Case, Shared ADC1 Ground

Figure 2-3. Typical Connection Diagram—DSP Use Case

#### Notes

- 1. A pull-up resistance of 10 k $\Omega$  or greater is recommended. R<sub>P I</sub> value can be determined by the  $\overline{IRQ}$  pin specification in Table 3-30.

- 2. R<sub>P I2C</sub> values can be determined by the I2C pull-up resistance specification in Table 3-25.

- 3. The headphone amplifier's output power and distortion ratings use the nominal capacitances shown. Larger capacitance reduces ripple on the internal amplifiers' supplies and, in turn, reduces distortion at high-output power levels. Smaller capacitance may not reduce ripple enough to achieve output power and distortion ratings. Because actual values of typical X7R/X5R ceramic capacitors deviate from nominal

values by a percentage specified in the manufacturer's data sheet, capacitors must be selected for maximum output power and minimum distortion required. Higher value capacitors than those shown may be used, however lower value capacitors must not (values can vary from the nominal by ±20%). A 0402-size or larger package is recommended.

- 4. Series resistance in the path of the power supplies must be avoided. Any voltage drop on charge pump fly nodes directly affects the charge-pump supplies and clips the audio output.

- 5. Lowering capacitance below the value shown affects PSRR, THD+N performance, ADC-DAC isolation and intermodulation, and interchannel isolation and intermodulation.

- 6. Connect to ground or a reference clock source.

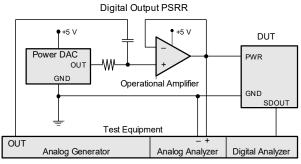

## 3 Characteristics and Specifications

Table 3-1 defines parameters as they are characterized in this section.

**Table 3-1. Parameter Definitions**

| Parameter                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel separation                              | Left-to-right and right-to-left channel separation is the difference in level between the active channel (driven to maximum full scale output) and the measured signal level in the idle channel at the test signal frequency. The active channel is configured and supplied with an appropriate input signal to drive a full scale output, with signal measured at the output of the associated idle channel.                                                                                                                                                                                                             |

| Common-mode rejection ratio (CMRR)              | The ratio of a specified input signal (applied to both sides of a differential input), relative to the output signal that results from it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Dynamic range                                   | The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth. A signal-to-noise ratio measurement over the specified bandwidth made with a –60 dB signal; 60 dB is added to resulting measurement to refer the measurement to full scale. This technique ensures that distortion components are below the noise level and do not affect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17–1991, and the Electronic Industries Association of Japan, EIAJ CP–307. Dynamic range is expressed in decibel units. |

| , ,                                             | The ratio of the rms value of all the spectral components of the muted output over the specified measurement bandwidth relative to a full-scale output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Gain drift                                      | The change in gain value with temperature, expressed in ppm/°C units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Gain accuracy                                   | The difference between the actual gain and the nominal gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Idle channel noise                              | The rms value of the signal with no input applied (properly back-terminated analog input, digital zero, or zero modulation input). Measured over the specified bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interchannel gain mismatch                      | The gain difference between left and right channel pairs. Interchannel gain mismatch is expressed in dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interchannel isolation                          | A measure of cross talk between the left and right channel pairs. Interchannel isolation is measured for each channel at the converter's output with no signal to the input under test and a full-scale signal applied to the other channel. Interchannel isolation is expressed in decibel units.                                                                                                                                                                                                                                                                                                                         |

| Load resistance and capacitance                 | The recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity. The load capacitance effectively moves the band-limiting pole of the amp in the output stage. Increasing load capacitance beyond the recommended value can cause the internal op-amp to become unstable.                                                                                                                                                                                                                                                                                     |

| Offset error                                    | The deviation of the midscale transition (111111 to 000000) from the ideal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output offset voltage                           | The DC offset voltage present at the amplifier's output when its input signal is in a mute state. The offset exists due to CMOS process limitations and is proportional to analog volume settings. When measuring the offset out the headphone amplifier, the headphone amplifier is ON.                                                                                                                                                                                                                                                                                                                                   |

| Total harmonic distortion (THD)                 | The ratio of the RMS sum of the harmonic distortion products in the specified bandwidth <sup>1</sup> relative to the RMS amplitude of the fundamental (i.e., test frequency) output.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Total harmonic<br>distortion +<br>noise (THD+N) | The ratio of the rms sum of distortion and noise spectral components across the specified bandwidth (typically 20 Hz–20 kHz or 20 Hz–80 kHz) relative to the rms value of the signal. THD+N is measured at –1 dBFS for the analog input and at 0 dB (or as otherwise specified in the table) for the analog output, as suggested in AES17–1991 Annex A. THD+N is expressed in decibel units.                                                                                                                                                                                                                               |

<sup>1.</sup>All performance measurements are specified with a 20 kHz low-pass brick-wall filter and, where noted, an A-weighted filter. The low-pass filter removes out-of-band noise.

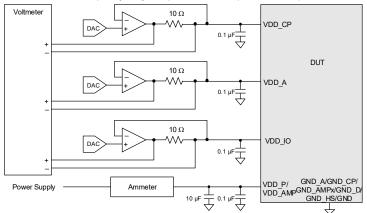

#### **Table 3-2. Recommended Operating Conditions**

Test conditions: Ground = GND\_A = GND\_D = GND\_CP = GND\_AMP1/2 = 0 V; voltages are with respect to ground.

|                | Parameter                              |                                                        | Symbol                 | Minimum   | Maximum | Unit |

|----------------|----------------------------------------|--------------------------------------------------------|------------------------|-----------|---------|------|

| DC power       | Charge pump                            |                                                        | VDD_CP                 | 1.66      | 1.94    | V    |

| supply         | LDO regulator for digital <sup>1</sup> | LDO_EN = 0                                             | VDD_D                  | 1.10      | 1.30    | V    |

|                | Serial interface control port          | 1.8 V nominal                                          | VDD_IO                 | 1.66      | 1.94    | V    |

|                | Analog                                 |                                                        | VDD_A                  | 1.66      | 1.94    | V    |

|                | Main power supply                      | Functional range <sup>2,3</sup>                        | VDD_P                  | 2.50      | 5.25    | V    |

|                |                                        | Parametric performance range 4                         |                        | 3.20      | 5.25    | V    |

|                |                                        | Parametric performance with<br>stereo HS MIC support 5 |                        | 3.30      | 5.25    | V    |

|                | Class D supplies                       |                                                        | VDD_AMP                | 4.75      | 5.25    | V    |

| External volta | ge applied to pin <sup>6,7</sup>       | TIP_SENSE pin                                          | V <sub>TIPSENSE</sub>  | CP_FILT_N | VDD_P   | V    |

|                |                                        | CP_FILT_P/N domain pins 8                              | $V_{CP\_FILT}$         | CP_FILT_N | VDD_P   | V    |

|                |                                        | VDD_IO domain pins                                     | $V_{VDD\_IO}$          | _ 0 _     | VDD_IO  | V    |

|                |                                        | VDD_A domain pins                                      | V <sub>VDD</sub> A     | 0         | VDD_A   | V    |

|                |                                        | VDD_P domain pins                                      | V <sub>VDD</sub> P     | 0         | VDD_P   | V    |

|                |                                        | RING_SENSE pin                                         | V <sub>RINGSENSE</sub> | 0         | VDD_P   | V    |

#### Table 3-2. Recommended Operating Conditions (Cont.)

Test conditions: Ground = GND\_A = GND\_D = GND\_CP = GND\_AMP1/2 = 0 V; voltages are with respect to ground.

| Parameter                |                                | Symbol         | Minimum    | Maximum | Unit |

|--------------------------|--------------------------------|----------------|------------|---------|------|

| Ambient temperature      | Functional range <sup>2</sup>  | T <sub>A</sub> | -40        | +85     | °C   |

|                          | Parametric performance range 4 |                | <b>–10</b> | +70     | °C   |

| VDD_AMP supply ramp rate |                                | _              | 0.0017     | 0.1     | V/µs |

**Note:** The device is fully functional and meets all parametric specifications in this section if operated within the specified conditions. Functionality and/or parametric performance are not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

- 1.If LDO\_EN is asserted, no external voltage must be applied to VDD\_D and VDD\_IO must be within the recommended operating range specified in Table 3-2. When LDO\_EN is asserted, the VDD\_D pin outputs 1.2 V. The minimum high input for LDO\_EN is 1.2 V. It can be connected to 1.2 V, 1.8 V, 3.3 V, or 5 V supplies to enable the LDO.

- 2. Defined as the range that the CS42L43 is capable of operating functionally, but may not meet all parametric specifications.

- 3. The following are affected when VDD\_P < 3.0 V: HSBIAS, charge pump LDO, TIP\_SENSE threshold, and RING\_SENSE threshold.

- 4. Defined as the range that the CS42L43 is capable of operating functionally, and meets all parametric specifications.

- 5. To support unplug detection of a stereo MIC jack if MICBIAS is set to 2.75 V, VDD P must be at least 3.3 V.

- 6. The maximum over/undervoltage is limited by the input current.

- 7. Section 1.2 and Section 1.4 list the power supply domain in which each CS42L43 pin resides.

- 8.CP FILT P/N is specified in Table 3-16.

#### Table 3-3. Absolute Maximum Ratings

Test conditions: Ground = GND A = GND D = GND CP = GND AMP1/2 = 0 V; voltages are with respect to ground.

|                                 | Parameter                                | Symbol                | Min  | Max  | Unit |

|---------------------------------|------------------------------------------|-----------------------|------|------|------|

| DC power supply                 | Charge pump, LDO, serial/control, analog | VDD_IO, VDD_A, VDD_CP | -0.3 | 2.33 | V    |

|                                 | Digital core                             | VDD_D                 | -0.3 | 1.55 | V    |

|                                 | Main power                               | VDD_P                 | -0.3 | 6.3  | V    |

|                                 | Class D                                  | VDD_ĀMP               | -0.3 | 6.3  | V    |

| Input current 1                 |                                          | l <sub>in</sub>       | _    | ±10  | mA   |

| Ambient operating temperature ( | (power applied)                          | T <sub>A</sub>        | -50  | +115 | °C   |

| Storage temperature             |                                          | T <sub>stg</sub>      | -65  | +150 | °C   |

Caution: Stresses beyond "Absolute Maximum Ratings" levels may cause permanent damage to the device. These levels are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3-2, "Recommended Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1.Any pin except supply pins. Transient currents of up to ±100 mA on analog input pins do not cause SCR latch-up.

#### Table 3-4. Combined ADC On-Chip Analog and Digital Filter Characteristics

Test conditions (unless specified otherwise): Signal inputs AC-coupled with 1  $\mu$ F; GND\_A = GND\_CP = 0 V; voltages are with respect to ground; typical performance data taken with VDD\_IO = VDD\_A = 1.8 V, VDD\_P = 3.3 V,  $T_A$  = +25°C; min/max performance data taken with VDD\_A = 1.66–1.94 V; VDD\_IO = 1.8 V, VDD\_P = 3.2–5.25 V,  $T_A$  = +25°C; DECIMn\_WNF\_EN = 0 and DECIMn\_HPF\_EN = 0; entire path characteristics including AFE + ADC + serial port.

|                                             | Parameter <sup>1</sup>                                                 |                 | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|------------------------------------------------------------------------|-----------------|---------|---------|---------|------|

| LPF passband (normalized to 28.33×10–3 •Fs) | Fs ≤ 48 kHz                                                            | -0.17 dB corner | 0.417   | _       | _       | Fs   |

| (normalized to 28.33×10 <sup>-3</sup> •Fs)  |                                                                        | –3 dB corner    | _       | 0.428   | _       | Fs   |

|                                             | Fs = 96 kHz                                                            | -0.38 dB corner | 0.417   | _       | _       | Fs   |

|                                             |                                                                        | –3 dB corner    | _       | 0.428   | -       | Fs   |

| Passband ripple                             |                                                                        | Fs ≤ 48 kHz     | -0.17   | _       | 0.11    | dB   |

| (DC to LPF passband corner; normalize       | (DC to LPF passband corner; normalized to 28.33×10 <sup>-3</sup> • Fs) |                 |         | _       | 0.2     | dB   |

| Transition band (0.5•Fs to 0.55•Fs)         |                                                                        |                 | 50      | _       | _       | dB   |

| Stopband attenuation 1 (0.55•Fs to 3•Fs     | ) <sup>2</sup>                                                         |                 | 80      | _       | _       | dB   |

| Stopband attenuation 2 (3•Fs to 10•Fs)      | 2                                                                      |                 | 120     | _       | _       | dB   |

| ADCn_INy_x-to-ASP_DOUT group dela           | y @1 kHz (ASP output)                                                  | Fs = 48 kHz     | _       | _       | 10/Fs   | S    |

|                                             |                                                                        | Fs = 96  kHz    | _       | _       | 10/Fs   | s    |

| ADCn_INy_x-to-SWIRE_DATAn group of          | Fs = 48 kHz                                                            | _               | _       | 11/Fs   | S       |      |

| output)                                     |                                                                        | Fs = 96 kHz     | _       | _       | 11/Fs   | S    |

<sup>1.</sup> Response scales with Fs (internal sample rate, based on MCLK\_IN). Specifications are normalized to Fs and are denormalized by multiplying by Fs.

<sup>2.</sup> Measurement is with high frequency out of band tone amplitude set to -24 dBFS with PGA setting = 0 dB and Fs = 48 kHz. Additionally, measurement may be limited by measuring equipment and/or noise floor.

#### Table 3-5. Combined PDM Input and On-Chip Digital Filter Characteristics

Test conditions (unless specified otherwise): GND\_A = GND\_CP = 0 V; voltages are with respect to ground; typical performance data taken with VDD\_IO = VDD\_A = 1.8 V, VDD\_P = 3.3 V,  $T_A = +25^{\circ}C$ ; min/max performance data taken with VDD\_A = 1.66–1.94 V; VDD\_IO = 1.8 V, VDD\_P = 3.2–5.25 V,  $T_A = +25^{\circ}C$ ; DECIMn\_WNF\_EN = 0 and DECIMn\_HPF\_EN = 0; entire path characteristics including decimators and serial port.

|                                                     | Parameter <sup>1</sup> |                                                                   | Minimum | Typical     | Maximum | Unit |

|-----------------------------------------------------|------------------------|-------------------------------------------------------------------|---------|-------------|---------|------|

| LPF passband                                        | Fs ≤ 48 kHz            | –0.17 dB corner                                                   | 0.417   |             | _       | Fs   |

| (normalized to 28.33×10 <sup>-3</sup> •Fs)          |                        | –3 dB corner                                                      | _       | 0.428       | _       | Fs   |

|                                                     | Fs = 96 kHz            | -0.38 dB corner                                                   | 0.417   |             | _       | Fs   |

|                                                     |                        | –3 dB corner                                                      | _       | 0.428       | _       | Fs   |

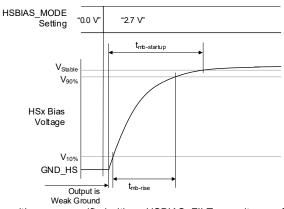

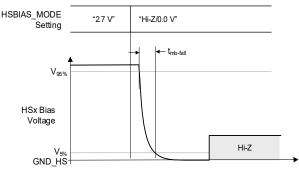

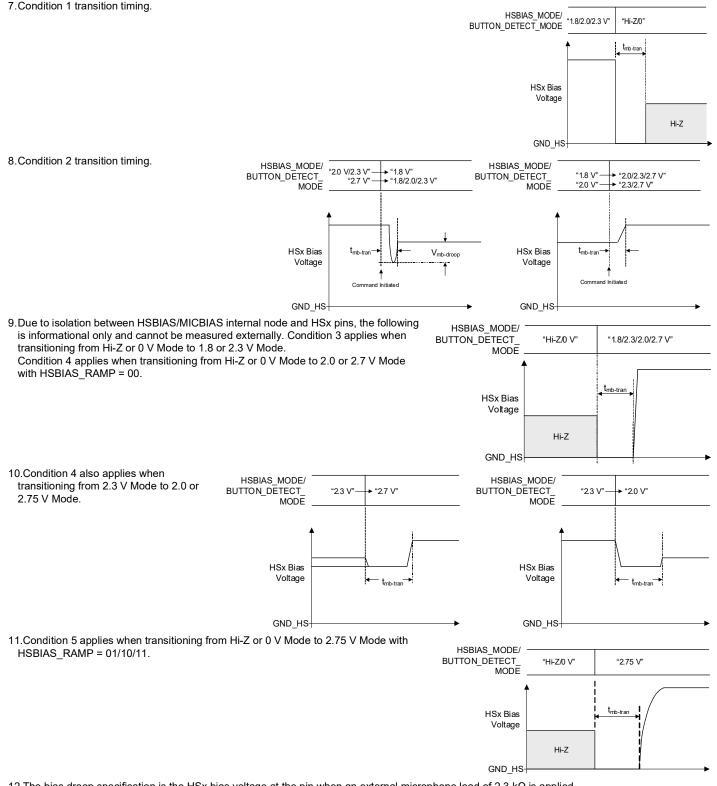

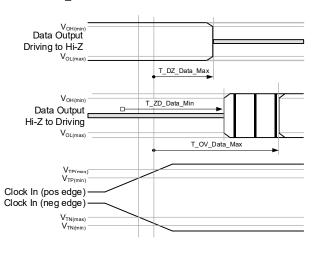

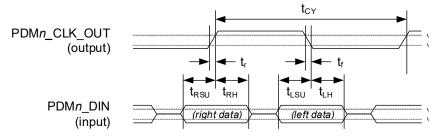

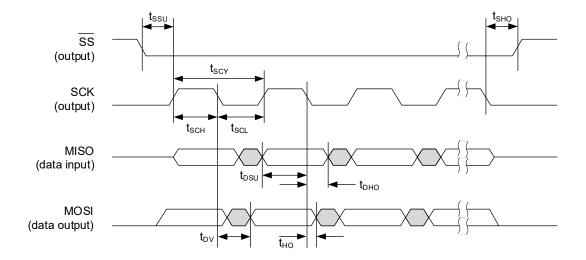

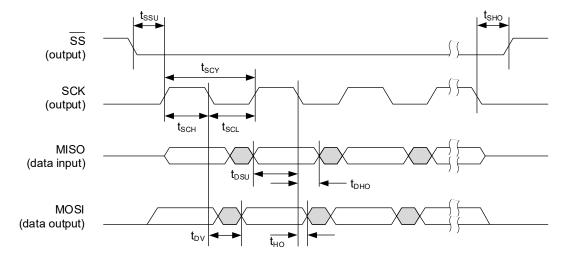

| Passband ripple                                     |                        | Fs ≤ 48 kHz                                                       | -0.17   |             | 0.11    | dB   |