# Advanced Haptic Driver with Integrated Boost, Waveform Memory, and Closed-Loop Algorithms

#### **Features**

- Closed-loop hardware and algorithms (SVC)

- Fast startup and braking for crisp/strong haptic feedback

- Extended actuator bandwidth supports textured effects

- Ensures consistent performance across actuator manufacturing variations, temperature, and aging

- Removes need for factory production-line calibration

- Integrated 15 V Class H boost converter

- Provides high output power for fast closed-loop response

- Enables consistent performance across battery conditions

- Supports multiple actuators driven in parallel (3  $\Omega$  minimum)

- Optimized low-latency and low-power hardware architecture

- Ultrafast wake-to-haptics enables imperceptible latency between touch/press events and haptic feedback

- Low-power Hibernate State with memory retention

- ROM/RAM-stored waveforms triggered by I<sup>2</sup>C/SPI/GPIO

- · Haptics waveform memory

- Simplifies system integration and reduces latency

- Enables software-configurable vehicles

- Stores PWLE and PCM waveforms in RAM

- AEC Q100 Grade-2 qualified for automotive applications, operating temperature –40 to 105°C

### **Specifications**

- 13.8 V<sub>PK</sub> output into 8 Ω load

- 3.0 V–15.0 V input supply

- · 15 V Class H boost converter

- · Ultra-low power

- 3.6 µA current consumption in Reset State

- 12 μA current consumption in Hibernate State

- Ultra-low latency

- 4.6 ms wake-to-haptics from Reset State

- 3.3 ms wake-to-haptics from Hibernate State

- Support for 1.8 V and 3.3 V digital input/output

- 34-pin wettable-flank QFN package, 4 × 4.5 mm, 0.4 mm pitch

### **Applications**

- · Virtual buttons/smart surfaces

- · Displays and interface panels

- Steering-wheel switches

- · HVAC control panel

- · Infotainment control panel

- · Door/window/seat controls

Important Notice: No license to any intellectual property right is included with this component, and certain uses or product designs, including certain haptics-related uses or haptics-system designs, may require an intellectual property license from one or more third parties.

Advanced Product Information

This document contains information for a product under development. Cirrus Logic reserves the right to modify this product without notice.

### **Haptic Driver Features**

- · Always on with ultra-low latency wakeup

- 4.6 ms wake-to-haptics from Reset State

- 3.3 ms wake-to-haptics from Hibernate State

- Class D architecture minimizes idle power consumption and switching losses

- 15 V driver supply voltage (maximum) from internal boost converter for fast startup and braking

- High performance with internal or external amplifier supply

13.8 V<sub>PK</sub> output into 8 Ω load

- Compatible with LRA/VCM impedances as low as 3  $\Omega$

- · Configurable amplifier output edge rate to reduce EMI

### **Monitoring Features**

- · Driver current monitoring via integrated sense circuit

- Driver voltage sensing via dedicated pins (VMON\_N/VMON\_P)

- · Current and voltage monitor data on I2S or TDM interface

### **Efficiency and Power Consumption**

- Internal boost operation from 3.0 V–15 V supply

- 89% overall efficiency (boost + amplifier) at 1 W output (8 Ω load, 5 V external supply)

- 3.6 µA current consumption in reset

- 12 μA current consumption in hibernate (RAM contents retained, monitoring for I<sup>2</sup>C or activity on GPIO/SPI pins)

### **Cirrus Logic Haptic Suite**

- System-level LRA/VCM actuator resonance frequency calibration

- Runtime haptics enables dynamic haptic-waveform generation with minimized delays

- Dynamic F<sub>0</sub> and Re<sub>DC</sub> tracking

- Driver voltage and current monitoring for software-triggered haptic actuator impedance and resonance frequency reporting

- Prestored (ROM or RAM) haptic waveforms triggerable by I2C/GPIO for user-interface events

- Flexible haptic-waveform generation

- I<sup>2</sup>C/GPIO-triggered haptic effects rendered at measured resonant frequency for optimum efficiency

- Haptic effects triggered by GPIO for virtual buttons on smart surfaces

- Compensation in click waveform playback for actuator unit-to-unit variation in resonant frequency and coil resistance

### **Digital Boost Converter Features**

- Programmable boost output voltage up to 15 V

- Advanced boost Class-H engine tracks audio envelope to maximize power efficiency

- Programmable boost inductor current limits up to 4 A

- Integrated boost and rectification FETs

- High-bandwidth digital control loop

- · Synchronous rectification in Active Mode

- Discontinuous Conduction Mode (DCM) for improved efficiency during low-power quiescent operation

### System Hardware Protection Features

- · IC thermal self-protection

- Boost/amplifier battery-brownout protection engine (BPE)

- Boost converter overvoltage/undervoltage protection

- VDD\_B/VBST undervoltage lockout (UVLO)

- Boost/amplifier short-circuit protection

- LRA/VCM protection

- Coil resistance monitoring

- Coil short-circuit detection

- DC input watchdog

### **Clocking and Data Interface Features**

- Clocks generated from audio serial port using internal phase-locked loop (PLL)

- Open-loop PLL mode for autonomous waveform playback with no external clock required

- Audio/haptic data serial port (ASP)

- Sample rates 8, 16, and 48 kHz

- I2S and TDM interface formats

- Configurable audio/data packet formatting

- Flexible clock rates and sample depth

- Tristate data output pin supports multi-device bus sharing

- I<sup>2</sup>C or SPI control port

- I<sup>2</sup>C High Speed, Fast-mode and Fast-mode Plus (Fm+) modes

- Up to eight unique I<sup>2</sup>C target address instances

- Supports I<sup>2</sup>C broadcast address to enable simultaneous code download to multiple devices

- SPI operation up to 17 MHz

- Multidevice synchronization and communication of device power-up and protection events

- Programmable and maskable interrupts with hardware interrupt pin (push-pull/open-drain) and software polling support

- GPIO pins with multiple features

- Optional external reference clock

- Device power up/down transitions

- Hardware trigger for buzz waveform playback

- Configurable by I<sup>2</sup>C or SPI interface or by DSP core

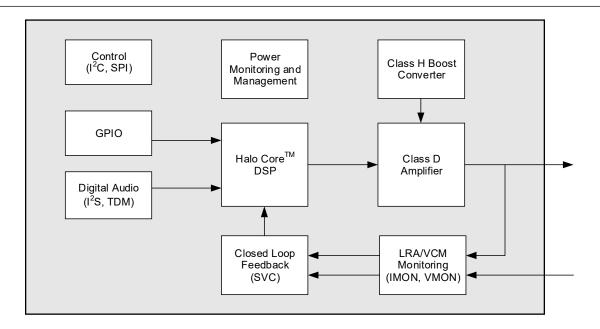

### **General Description**

The CS40L5x integrates a self-contained haptic signal generator and driver, optimized for high-definition haptic smart surfaces, steering wheels, interactive displays, and car-seat applications. The hardware and the digital signal processing are resonance-aware and designed specifically for optimal drive of highly resonant linear resonant actuators (LRAs) and voice coil motors (VCMs).

The CS40L5x incorporates a 130 MIPS Halo Core<sup>TM</sup> DSP, which is used to execute the haptic-control algorithms. Waveforms are stored in ROM or RAM to match the LRA/VCM characteristics. Ultra-low power reset and hibernate states enable always-on operation with fast wake-up via GPIO. ROM-defined waveforms can be output within 4.6 ms of wake up from reset. Additional waveforms can be downloaded to RAM during run time; these are retained in the low-power Hibernate State and can be output within 3.3 ms of wake-up from hibernate. Runtime haptic-waveform synthesis allows application-specific waveforms to be generated using PCM or PWLE-coded parameters.

The CS40L51/52/53 devices support different algorithm features:

| Feature                                                 | CS40L51       | CS40L52 | CS40L53 |

|---------------------------------------------------------|---------------|---------|---------|

| Calibration (R <sub>E</sub> and F <sub>0</sub> )        | Yes           | Yes     | Yes     |

| Click compensation (R <sub>E</sub> and F <sub>0</sub> ) | Yes           | Yes     | Yes     |

| Haptics synthesizer                                     | Yes           | Yes     | Yes     |

| Runtime haptics (RTH)                                   | Yes           | Yes     | Yes     |

| Load diagnostics                                        | Yes           | Yes     | _       |

| Closed-loop algorithms (SVC)                            | Yes           | Yes     | _       |

| Audio to haptics (A2H)                                  | Yes           | _       | _       |

| Live F <sub>0</sub> tracking (LF0T)                     | Yes           | _       | _       |

| Active vibration compensation                           | Yes           | _       | _       |

| Wavetable sample rate                                   | 8 kHz, 24 kHz | 8 kHz   | 8 kHz   |

The Class D amplifier supports supply voltages up to 15.0 V. The amplifier incorporates an advanced closed-loop architecture and a differential output stage. The digitally controlled boost converter supports Class-H tracking and generates up to 15 V output from typical system supply rails (e.g., 5 V or 12 V). The CS40L5x delivers up to 13.8  $V_{PK}$  into an 8  $\Omega$  load.

The CS40L5x includes self-protection and system-protection features. The boost and driver stages are protected against short circuits; IC over-temperature shutdown protection is provided in hardware. The input voltage is continuously monitored. The boost converter and driver gain are automatically adjusted for the supply voltage according to programmable voltage/current thresholds; the adjustment of the driver is integrated with the IC thermal protection, ensuring seamless gain adjustment if necessary.

The CS40L5x is available in a commercial-grade 0.4 mm pitch, 34-pin wettable-flank QFN package for operation from –40° to +105°C. The CS40L5x is AEC-Q100 Grade 2 qualified for automotive applications.

See Section 6 for ordering information.

#### **Table of Contents**

| 1 Pin Assignments and Descriptions                                  | 4    |

|---------------------------------------------------------------------|------|

| 1.1 34-Pin QFN (Top View. Through-Package)                          | 4    |

| 1.1 34-Pin QFN (Top View, Through-Package) 1.2 QFN Pin Descriptions | 5    |

| 2 Typical Connection Diagram                                        | 7    |

| 3 Characteristics and Specifications                                |      |

| Table 3-1. Recommended Operating Conditions                         |      |

| Table 3-2. Absolute Maximum Ratings                                 | 🤉    |

| 4 Package Dimensions                                                | . 10 |

| 5 Package Marking                                                   | . 11 |

| 6 Ordering Information                                              |      |

| 7 Revision History                                                  |      |

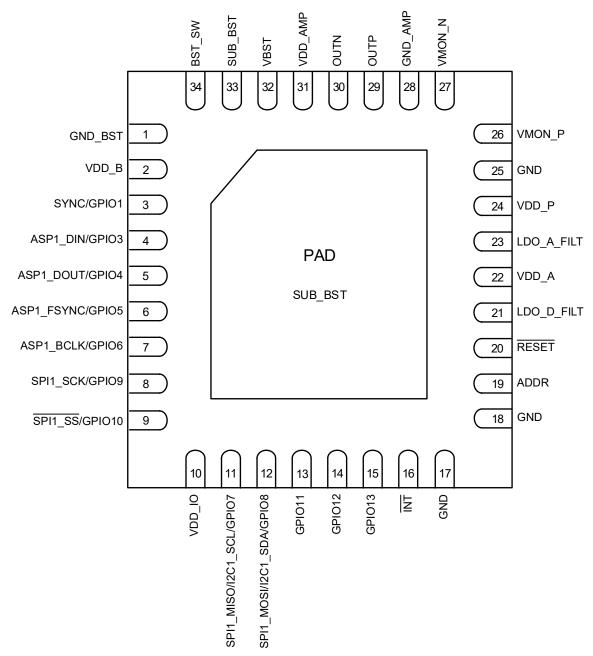

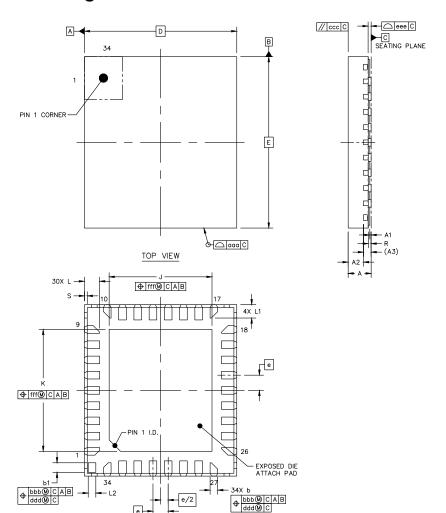

### 1 Pin Assignments and Descriptions

### 1.1 34-Pin QFN (Top View, Through-Package)

Figure 1-1. QFN 34-pin diagram (Top View, Through Package)

## 1.2 QFN Pin Descriptions

Table 1-1. QFN Pin Descriptions

| Pin Name                     | n Name Pin # Power I/O Description |            | Internal<br>Connection | State at<br>Reset                                                                                                                                                                                                  |                                         |                                 |

|------------------------------|------------------------------------|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------|

|                              |                                    |            |                        | Digital I/O                                                                                                                                                                                                        |                                         |                                 |

| ASP1_BCLK/GPIO6              | 7                                  | VDD_IO     | I/O                    | Audio Serial Port Bit Clock. Serial shift clock for ASP interface. Optional clock reference for PLL.  GPIO6. General-purpose input/output.                                                                         | Programmable<br>(pull-up,<br>pull-down) | Input,<br>passive<br>pull down  |

| ASP1_DIN/GPIO3               | 4                                  | VDD_IO     | I/O                    | Audio Serial Port Data Input. Serial data input for ASP interface.  GPIO3. General-purpose input/output.                                                                                                           | Programmable<br>(pull-up,<br>pull-down) | Input,<br>passive<br>pull down  |

| ASP1_DOUT/GPIO4              | 5                                  | VDD_IO     | I/O                    | Audio Serial Port Data Output. Serial data output for ASP interface.  GPIO4. General-purpose input/output.                                                                                                         | Programmable<br>(pull-up,<br>pull-down) | Output,<br>passive<br>pull down |

| ASP1_FSYNC/GPIO5             | 6                                  | VDD_IO     | I/O                    | Audio Serial Port Frame Sync. Frame sync for ASP interface. Optional clock source for PLL.  GPIO5. General-purpose input/output.                                                                                   | Programmable<br>(pull-up,<br>pull-down) | Input,<br>passive<br>pull down  |

| GPIO13                       | 15                                 | VDD_IO     | I/O                    | GPIO13. General-purpose input/output.  MCLK. External clock reference input.  WAKE. External trigger to wake from Hibernate State.                                                                                 | Programmable<br>(pull-up,<br>pull-down) | Input,<br>Hi-Z                  |

| ĪNT                          | 16                                 | VDD_IO     | I/O                    | Interrupt. Programmable open-drain interrupt output.                                                                                                                                                               | Programmable<br>(pull-up,<br>pull-down) | Output,<br>Hi-Z                 |

| RESET                        | 20                                 | See Note 1 | I                      | Reset. Active-low reset input.                                                                                                                                                                                     | _                                       | Input                           |

| SPI1_MISO/I2C1_SCL/<br>GPI07 | 11                                 | VDD_IO     | I/O                    | SPI Control-Port Master In Slave Out. SPI data input. I2C Control-Port Clock. Clock input for the I2C interface. GPIO7. General-purpose input/output.  WAKE. External trigger to wake from Hibernate State.        | Programmable<br>(pull-up,<br>pull-down) | Input,<br>Hi-Z                  |

| SPI1_MOSI/I2C1_SDA/<br>GPI08 | 12                                 | VDD_IO     | I/O                    | SPI Control-Port Master Out Slave In. SPI data output. I2C Control-Port Data. Data input/output for the I2C interface.  GPIO8. General-purpose input/output.  WAKE. External trigger to wake from Hibernate State. | Programmable<br>(pull-up,<br>pull-down) | Output,<br>Hi-Z                 |

| SPI1_SCK/GPIO9               | 8                                  | VDD_IO     | I/O                    | SPI Control-Port Clock. Clock input for the SPI interface. GPIO9. General-purpose output.                                                                                                                          | Programmable<br>(pull-up,<br>pull-down) | Input,<br>passive<br>pull down  |

| SPI1_SS/GPIO10               | 9                                  | VDD_IO     | I/O                    | SPI Control-Port Slave Select. Active-low Slave Select input for the SPI interface.  GPIO10. General-purpose input/output.                                                                                         | Programmable<br>(pull-up,<br>pull-down) | Input,<br>Hi-Z                  |

| GPIO11                       | 13                                 | VDD_IO     | I/O                    | GPIO11. General-purpose input/output.  MCLK. External clock reference input.  WAKE. External trigger to wake from Hibernate State.                                                                                 | Programmable<br>(pull-up,<br>pull-down) | Input,<br>Hi-Z                  |

| GPIO12                       | 14                                 | VDD_IO     | I/O                    | GPIO12. General-purpose input/output. WAKE. External trigger to wake from Hibernate State.                                                                                                                         | Programmable<br>(pull-up,<br>pull-down) | Input,<br>Hi-Z                  |

| SYNC/GPIO1                   | 3                                  | VDD_IO     | I/O                    | Multidevice Synchronization. Serial data bus connecting devices in multi-channel applications.  GPIO1. General-purpose input/output.  MCLK. External clock reference input.                                        | Programmable<br>(pull-up,<br>pull-down) | Input,<br>passive<br>pull down  |

|                              |                                    |            |                        | Analog I/O                                                                                                                                                                                                         |                                         |                                 |

| ADDR                         | 19                                 | VDD_A      | ı                      | I2C Address Input. Address pin for I2C Target address. Latched on POR or hard reset.                                                                                                                               | _                                       | _                               |

| BST_SW                       | 34                                 |            | ı                      | Boost Switch. Input to internal boost FETs.                                                                                                                                                                        |                                         |                                 |

| LDO_A_FILT                   | 23                                 | VDD_P      | 0                      | <b>LDO_A Output.</b> Decoupling point for analog supply (if powered from internal LDO).                                                                                                                            | _                                       | _                               |

### Table 1-1. QFN Pin Descriptions (Cont.)

| Pin Name   | Pin #            | Power<br>Supply | I/O | Description                                                                                                                                               | Internal<br>Connection | State at<br>Reset |

|------------|------------------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| LDO_D_FILT | 21               | VDD_A           | 0   | <b>LDO_D Output.</b> Decoupling point for digital supply, powered from LDO_D.                                                                             | _                      | _                 |

| OUTN       | 30               | VDD_AMP         | 0   | Differential Output. Internal Class D amplifier output.                                                                                                   | _                      | _                 |

| OUTP       | 29               | VDD_AMP         | 0   | Differential Output. Internal Class D amplifier output.                                                                                                   | _                      | _                 |

| VBST       | 32               | _               | 0   | <b>Boosted Supply from Boost Converter.</b> Internal boost converter output.                                                                              | _                      | _                 |

| VMON_N     | 27               | VDD_AMP         | I   | Output Monitor. Voltage-sense input for OUTN. Must be connected to OUTN via 4.99 k $\Omega$ (1%) resistor.                                                | _                      | _                 |

| VMON_P     | 26               | VDD_AMP         | I   | Output Monitor. Voltage-sense input for OUTP. Must be connected to OUTP via 4.99 k $\Omega$ (1%) resistor.                                                | _                      | _                 |

|            |                  |                 |     | Power Supplies                                                                                                                                            |                        |                   |

| GND        | 17,<br>18,<br>25 | _               | _   | <b>Note: Analog and Digital Ground.</b> Ground return for the analog and digital functional blocks throughout the device.                                 | _                      | _                 |

| GND_AMP    | 28               | _               | _   | <b>Power Ground.</b> Ground reference for the Class D amplifier output stage.                                                                             | _                      | _                 |

| GND_BST    | 1                | _               | _   | <b>Boost Converter Power Ground.</b> Ground reference for the boost converter.                                                                            | _                      | _                 |

| SUB_BST    | 33,<br>PAD       | _               | _   | <b>Boost Substrate Ground and Thermal Pad.</b> The thermal pad must be connected to ground.                                                               | _                      | _                 |

| VDD_A      | 22               | _               | I   | <b>Analog Supply.</b> Power supply for the internal analog circuits. Also powers digital circuits via internal regulator.                                 | _                      | _                 |

| VDD_P      | 24               | _               | 1   | <b>System Supply.</b> Power supply for always-on (Hibernate) circuits. Also powers the LDO_A regulator, which can be used to generate the VDD_A supply.   | _                      | _                 |

| VDD_AMP    | 31               | _               | ı   | Amplifier Supply. Power supply for the Class D amplifier.                                                                                                 |                        | _                 |

| VDD_B      | 2                | _               | I   | <b>Boost Supply.</b> Power supply for boost converter. (Note this is primarily a monitor pin; the boost current is conducted via the inductor to BST_SW.) | _                      | _                 |

| VDD_IO     | 10               | _               | I   | Digital I/O Supply. Power supply for digital input/output.                                                                                                | _                      | _                 |

<sup>1.5</sup> V-tolerant input, supply-independent

Copyright © 2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

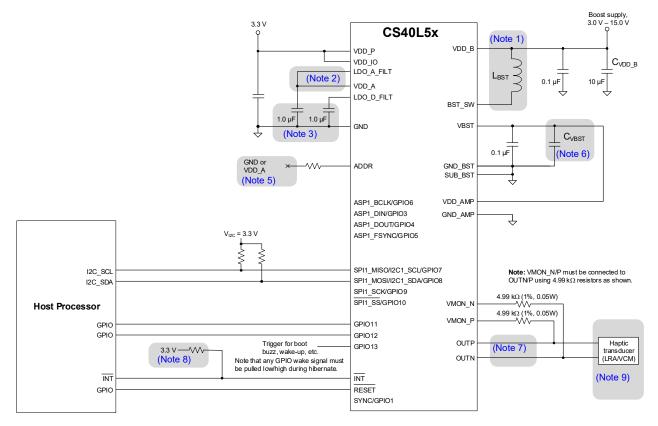

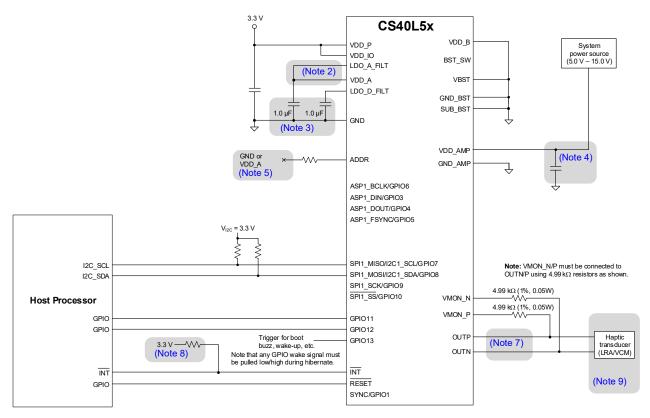

### 2 Typical Connection Diagram

Figure 2-1. Typical configuration with internal boost power source

Figure 2-2. Typical configuration with external amplifier power source

PA1001R1 7

### Notes referenced in the typical connection diagrams:

- 1. The  $L_{BST}$  inductor must not derate to a value less than 0.5  $\mu$ H. Inductance of 1.0  $\mu$ H is recommended for typical applications.

- 2. In the configuration shown, the LDO\_A regulator is used to generate the analog supply. The VDD\_A supply pin is connected to the LDO output, LDO A FILT.

- 3. The LDO\_A\_FILT capacitor must not de-rate to a value less than 500 nF at 1.8 V. The LDO\_D\_FILT capacitor must not de-rate to a value less than 390 nF at 1.25 V.

- 4. The  $C_{VDD\ AMP}$  capacitor must not derate to a value less than 2  $\mu F$  at 15 V.

- 5. The I<sup>2</sup>C device address are configured using a resistor connected between the ADDR pin and GND, or else between the ADDR pin and VDD A. The capacitive loading on the ADDR pin must not exceed 100 pF.

- 6. The C<sub>VBST</sub> capacitor must not derate to a value less than 2 μF at 15 V.

- 7. Optional EMI-suppression capacitors between OUTx and GND\_AMP may be used, depending on the application requirements. The capacitance should not exceed 470 pF, as higher capacitance increases switching losses.

- 8. In the configuration shown, the CS40L5x INT pin is configured as an open-drain output and an external pull-up resistor (e.g.,  $100 \text{ k}\Omega$ ) to VDD\_IO is required.

- 9. When using a simulated load of 8  $\Omega$  + 33  $\mu$ H, a Coilcraft DO5040H–333MLB inductor is used.

#### General notes and recommendations:

- Fig. 2-1 through Fig. 2-2 are examples intended to describe the connectivity of each functional block within the CS40L5x, and do not limit all possible use cases.

- All external passive component values listed are nominal values.

### 3 Characteristics and Specifications

**Note:** The default register field configurations are used unless specified otherwise in the test conditions.

#### Table 3-1. Recommended Operating Conditions

Test conditions (unless specified otherwise): Ground = GND = GND AMP = GND BST = 0 V; voltages are with respect to ground.

|                | Parameter <sup>1</sup>             |                      | Symbol          | Minimum       | Maximum | Unit |

|----------------|------------------------------------|----------------------|-----------------|---------------|---------|------|

| DC power       | Analog and digital supply          |                      | VDD_P           | 3.0           | 5.5     | V    |

| supply         | Digital I/O supply                 |                      | VDD_IO          | 1.71          | 3.6     | V    |

|                | Analog supply <sup>2</sup>         |                      | VDD_A           | 1.71          | 1.89    | V    |

|                | Boost converter 3, 4               |                      | VDD_B           | 3.0           | 15.0    | V    |

|                | Amplifier supply 5, 6              |                      | VDD_AMP         | 5.0           | 15.0    | V    |

| Supply ramp    | up/down                            | t <sub>PWR-UD</sub>  | 0.1             | 100           | ms      |      |

|                |                                    | VDD_B, VDD_AMP       |                 | 0.2           | 100     | ms   |

| External volta | ge applied to digital input/output | V <sub>INDI</sub>    | -0.3            | VDD_IO + 0.3  | V       |      |

|                |                                    | RESET pin            |                 | -0.3          | 5.5     | V    |

| External volta | ge applied to analog inputs        | $V_{INAI}$           | -0.3            | VDD_A + 0.3   | V       |      |

| External volta | ge applied to analog inputs        | V <sub>IN-VMON</sub> | -0.3            | VDD_AMP + 0.3 | V       |      |

| External volta | ge applied to analog outputs       | V <sub>IN-OUTx</sub> | -0.3            | VDD_AMP + 0.3 |         |      |

| Ambient temp   | perature                           | T <sub>A</sub>       | <del>-4</del> 0 | +105          | °C      |      |

**Note:** The device is fully functional and meets all parametric specifications in this section if operated within the specified conditions. Functionality and parametric performance is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

- 1. There are no sequencing requirements associated with any of the supplies—each can be enabled or removed independently of the other supplies.

- 2. The analog supply can be generated by the internal LDO (powered from VDD\_P), or else provided externally. If the LDO is used, the VDD\_A pin must be connected to the LDO output pin (LDO\_A\_FILT) and must not be connected to any external supply.

- 3. Note VDD\_B is the voltage-monitor point for the boost converter; the load current path is through the inductor to the BST\_SW.

- 4. If the amplifier is powered directly using an external supply to VDD\_AMP, the VDD\_B supply is not required.

- 5. The amplifier supply can be generated by the boost converter, or else provided externally. If the boost converter is used, the VDD\_AMP pin must be connected to the boost-converter output pin, VBST.

- 6.Note the VDD AMP voltage may exceed these operating limits if generated by the CS40L5x boost converter.

- 7.All digital I/O pins except RESET.

#### Table 3-2. Absolute Maximum Ratings

Test conditions (unless specified otherwise): Ground = GND = GND AMP = GND BST = 0 V; voltages are with respect to ground.

|                      | Parameter                                   |                       | Symbol          | Minimum     | Maximum | Unit |

|----------------------|---------------------------------------------|-----------------------|-----------------|-------------|---------|------|

| DC power supply      | Analog and digital supply                   |                       | VDD_P           | -0.3        | 6       | V    |

|                      | Digital I/O supply                          | VDD_IO                | -0.3            | 4.32        | V       |      |

|                      | Analog supply                               |                       | VDD_A           | -0.3        | 2.27    | V    |

|                      | Boost converter                             |                       | VDD_B           | -0.3        | 18      | V    |

|                      | Amplifier supply                            |                       | VDD_AMP         | VDD_B - 0.3 | 18      | V    |

| Input current        |                                             | digital I/O (per pin) | l <sub>in</sub> | _           | ±10     | mA   |

|                      |                                             | ADDR pin              |                 | _           | ±10     | mΑ   |

| Output load impeda   | nce                                         |                       | Z <sub>L1</sub> | 3           | _       | Ω    |

| Ambient operating t  | emperature (local to device, power applied) | T <sub>A</sub>        | <del>-</del> 50 | +115        | °C      |      |

| Junction operating t | emperature (power applied)                  | $T_J$                 | -40             | +150        | °C      |      |

| Storage temperatur   | T <sub>STG</sub>                            | <del>-</del> 65       | +150            | °C          |         |      |

Caution: Stresses beyond "Absolute Maximum Ratings" levels may cause permanent damage to the device. These levels are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3-1, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

PA1001R1 9

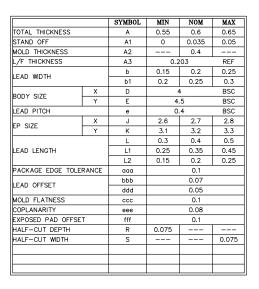

### 4 Package Dimensions

- 1.0 COPLANARITY APPLIES TO LEADS, CORNER LEADS AND DIE ATTACH PAD. 2.0 TOTAL THICKNESS NOT INCLUDE SAW BURR. 3.0 STEP CUT TYPE.

Figure 4-1. Wettable-Flank QFN Package Drawing

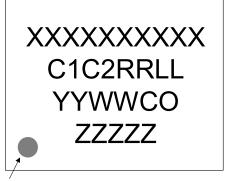

### 5 Package Marking

Pin 1 Location Indicator

#### Top Side Brand

Line 1: Part number Line 2: Package mark Line 3: Package mark

Line 4: Encoded wafer/device ID

#### Package Mark Fields

C1 = Cirrus Logic Index Code 1 C2 = Cirrus Logic Index Code 2 RR = Device revision code LL = Lot sequence code YY = Year of manufacture WW = Work week of manufacture CO = Country of origin (CO)

Figure 5-1. Package Marking

### **6 Ordering Information**

Table 6-1. Ordering Information

| Product | Description                                                                                        | Package    | RoHS<br>Compliant | Grade        | Temperature<br>Range | Container        | Orderable Part<br>Number |

|---------|----------------------------------------------------------------------------------------------------|------------|-------------------|--------------|----------------------|------------------|--------------------------|

| CS40L51 | Advanced Haptic Driver<br>with Integrated Boost,<br>Waveform Memory, and<br>Closed-Loop Algorithms | 34-pin QFN | Yes               | Commercial 1 | -40 to +105°C        | Tape and<br>Reel | CS40L51-ENR              |

| CS40L52 | Advanced Haptic Driver<br>with Integrated Boost,<br>Waveform Memory, and<br>Closed-Loop Algorithms | 34-pin QFN | Yes               | Commercial 1 | –40 to +105°C        | Tape and<br>Reel | CS40L52-ENR              |

| CS40L53 | Advanced Haptic Driver<br>with Integrated Boost,<br>Waveform Memory, and<br>Closed-Loop Algorithms | 34-pin QFN | Yes               | Commercial 1 | –40 to +105°C        | Tape and<br>Reel | CS40L53-ENR              |

<sup>1.</sup>AEC-Q100 Grade 2 qualified

### 7 Revision History

Table 7-1. Revision History

| Revision | Changes         |

|----------|-----------------|

| R1       | Initial version |

| MAY 2025 |                 |

**Important:** Please check www.cirrus.com or with your Cirrus Logic sales representative to confirm that you are using the latest revision of this document and to determine whether there are errata associated with this device.

### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative. To find one nearest you, go to www.cirrus.com.

#### IMPORTANT NOTICE

"Advance" product information describes products that are in development and subject to substantial development changes. For the purposes of our terms and conditions of sale, "Preliminary" or "Advanced" datasheets are nonfinal datasheets that include, but are not limited to, datasheets marked as "Target", "Advance", "Product Preview", "Preliminary Technical Data" and/or "Preproduction." Products provided with any such datasheet are therefore subject to relevant terms and conditions associated with "Preliminary" or "Advanced" designations, as set out in our terms and conditions of sale, including but not limited to that Cirrus Logic expressly disclaims any warranties with respect to such products. The products and services of Cirrus Logic International (UK) Limited; Cirrus Logic, Inc.; and other companies in the Cirrus Logic group (collectively either "Cirrus Logic" or "Cirrus") are sold subject to Cirrus Logic's terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. Software is provided pursuant to applicable license terms. Cirrus Logic reserves the right to make changes to its products and specifications or to discontinue any product or service without notice. Customers should therefore obtain the latest version of relevant information from Cirrus Logic to verify that the information is current and complete. Testing and other quality control techniques are utilized to the extent Cirrus Logic deems necessary. Specific testing of all parameters of each device is not necessarily performed. In order to minimize risks associated with customer applications, the customer must use adequate design and operating safeguards to minimize inherent or procedural hazards. Cirrus Logic is not liable for applications assistance or customer product design. The customer is solely responsible for its overall product design, end-use applications, and system security, including the specific manner in which it uses Cirrus Logic c

CIRRUS LOGIC PRODUCTS ARE NOT DESIGNED, TESTED, INTENDED OR WARRANTED FOR USE (1) WITH OR IN IMPLANTABLE PRODUCTS OR FDA/MHRA CLASS III (OR EQUIVALENT CLASSIFICATION) MEDICAL DEVICES, OR (2) IN ANY PRODUCTS, APPLICATIONS OR SYSTEMS, INCLUDING WITHOUT LIMITATION LIFE-CRITICAL MEDICAL EQUIPMENT OR SAFETY OR SECURITY EQUIPMENT, WHERE MALFUNCTION OF THE PRODUCT COULD CAUSE PERSONAL INJURY, DEATH, SEVERE PROPERTY DAMAGE OR SEVERE ENVIRONMENTAL HARM. INCLUSION OF CIRRUS LOGIC PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS LOGIC DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS LOGIC PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS LOGIC PRODUCTS IN SUCH A MANNER, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS LOGIC, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

This document is the property of Cirrus Logic, and you may not use this document in connection with any legal analysis concerning Cirrus Logic products described herein. No license to any technology or intellectual property right of Cirrus Logic or any third party is granted herein, including but not limited to any patent right, copyright, mask work right, or other intellectual property rights. Any provision or publication of any third party's products or services does not constitute Cirrus Logic's approval, license, warranty or endorsement thereof. Cirrus Logic gives consent for copies to be made of the information contained herein only for use within your organization with respect to Cirrus Logic integrated circuits or other products of Cirrus Logic, and only if the reproduction is without alteration and is accompanied by all associated copyright, proprietary and other notices and conditions (including this notice). This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. This document and its information is provided "AS IS" without warranty of any kind (express or implied). All statutory warranties and conditions are excluded to the fullest extent possible. No responsibility is assumed by Cirrus Logic for the use of information herein, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. Cirrus Logic, Cirrus, the Cirrus Logic logo design, SoundClear, and Halo Core are among the trademarks of Cirrus Logic. Other brand and product names may be trademarks or service marks of their respective owners.

Copyright © 2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd. All rights reserved.

SPI is a trademark of Motorola.